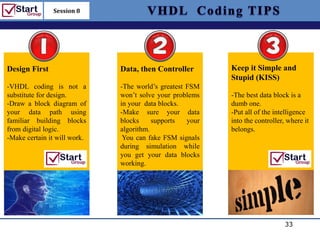

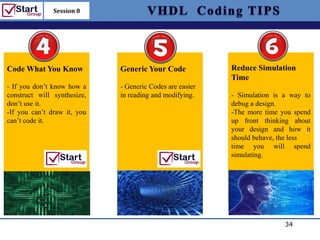

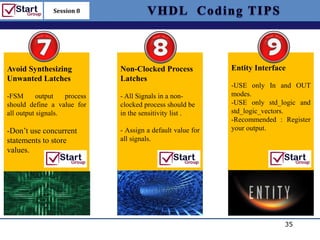

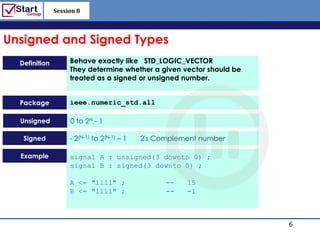

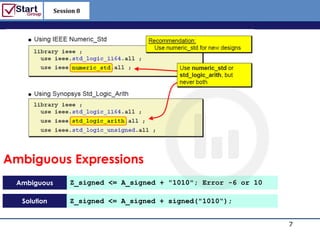

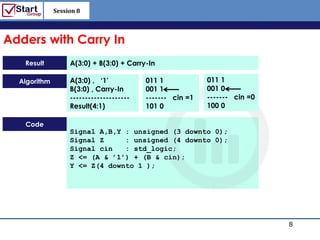

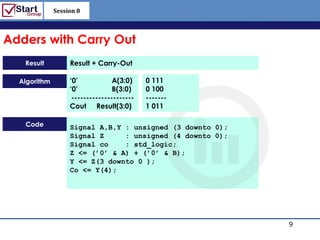

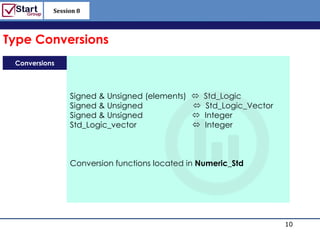

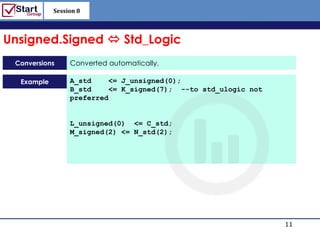

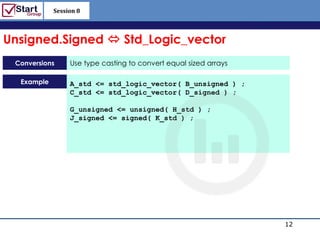

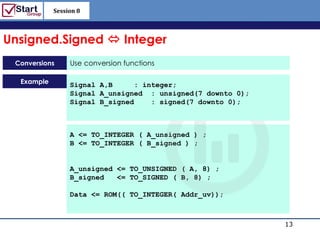

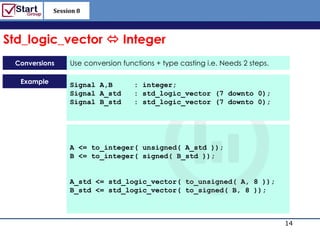

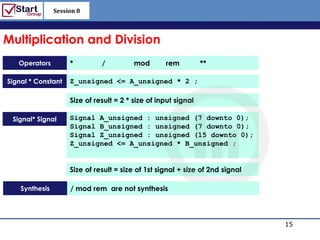

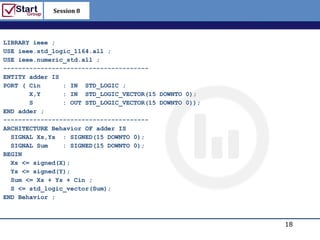

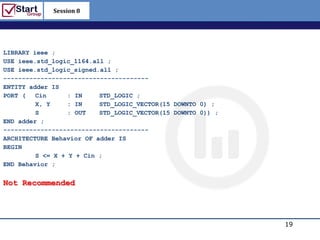

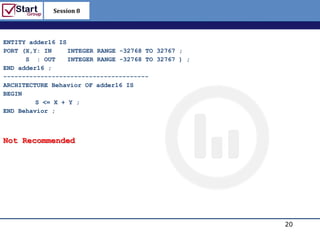

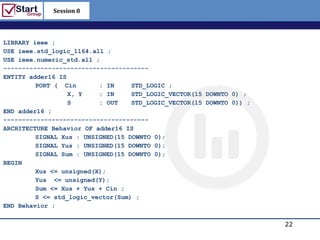

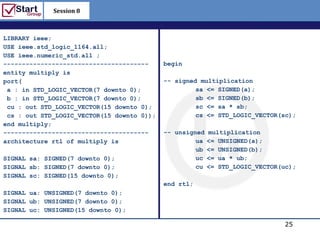

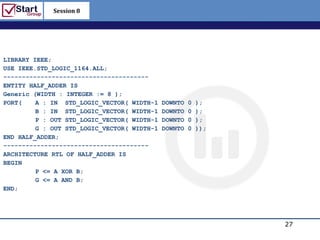

The document discusses VHDL coding techniques including designing first before coding, keeping data and controller blocks separate, keeping designs simple, coding what is understood, using generics to make code reusable, and reducing simulation time to efficiently debug designs. It also provides code examples for arithmetic circuits, data type conversions, and basic logic gates.

![http://www.bized.co.uk

- Evaluation Test

8

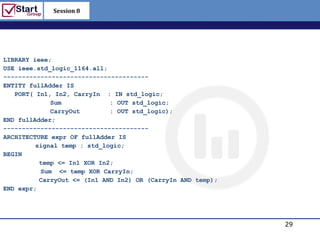

- Arithmetic Circuits

Contents - Tutorial [2]

- IP Cores

- ISIM Simulator

- Language Templates

- VHDL Coding TIPS

2

Copyright 2006 – Biz/ed](https://image.slidesharecdn.com/sessioneight-111216135537-phpapp02/85/Session-eight-2-320.jpg)

![http://www.bized.co.uk

Next Part is inside Start Group tutorial [2]

Start Group tutorial [2]

Prepared by

Alaa Salah Shehata

Mahmoud A. M. Abd El Latif

Mohamed Mohamed Tala’t

Mohamed Salah Mahmoud

Version 02 – October 2011

Copyright 2006 – Biz/ed](https://image.slidesharecdn.com/sessioneight-111216135537-phpapp02/85/Session-eight-31-320.jpg)