The document discusses sequential logic implementation including finite state machines (FSMs). It covers FSM design procedures like deriving state diagrams and transition tables from specifications. It also compares Moore and Mealy machines, noting that Moore machines have outputs depend only on current state while Mealy machines have outputs depend on current state and inputs. Mealy machines tend to require fewer states but Moore machines are safer to use in designs where outputs change at clock edges. The document provides examples of specifying and implementing FSMs in Verilog including both Moore and Mealy machines. It also gives an example FSM design for a vending machine.

![Verilog FSM - Reduce 1s Example

! Change the first 1 to 0 in each string of 1’s zero

" Example Moore machine implementation [0]

1 0

// State assignment 0 one1

parameter zero = 0, one1 = 1, two1s = 2;

[0]

module reduce (out, clk, reset, in); 0 1

output out;

1

input clk, reset, in;

reg out; two1s

reg [1:0] state; // state register [1]

reg [1:0] next_state;

CS 150 - Spring 2007 – Lec #7: Sequential Implementation – 9

Moore Verilog FSM (cont’d)

always @(in or state)

case (state)

zero

zero: begin // last input was a zero [0]

out = 0;

if (in) next_state = one1; 1 0

else next_state = zero;

end 0 one1

[0]

one1: begin // we've seen one 1

out = 0; 0 1

if (in) next_state = two1s; 1

else next_state = zero; two1s

end [1]

two1s: begin // we've seen at least 2 ones

out = 1;

if (in) next_state = two1s;

else next_state = zero;

include all signals

end that are input to state

and output equations

default: begin // in case we reach a bad state

out = 0;

next_state = zero;

endcase

CS 150 - Spring 2007 – Lec #7: Sequential Implementation – 10](https://image.slidesharecdn.com/sequentiallogicimplementation-130322091318-phpapp01/85/Sequential-logic-implementation-5-320.jpg)

![Moore Verilog FSM (cont’d)

// Implement the state register

always @(posedge clk) zero

if (reset) state <= zero; [0]

else state <= next_state;

1 0

endmodule

0 one1

[0]

0 1

1

two1s

[1]

CS 150 - Spring 2007 – Lec #7: Sequential Implementation – 11

Mealy Verilog FSM for Reduce-1s Example

module reduce (clk, reset, in, out);

input clk, reset, in; output out;

reg out; reg state; // state register

0/0

reg next_state;

parameter zero = 0, one = 1; zero

always @(in or state)

case (state) 0/0 1/0

zero: begin // last input was a zero

if (in) next_state = one;

else next_state = zero; one1

out = 0; 1/1

end

one: // we've seen one 1

if (in) begin

next_state = one;

out = 1;

end

else begin

next_state = zero;

out = 0;

end

endcase

always @(posedge clk)

if (reset) state <= zero;

else state <= next_state;

endmodule CS 150 - Spring 2007 – Lec #7: Sequential Implementation – 12

7](https://image.slidesharecdn.com/sequentiallogicimplementation-130322091318-phpapp01/85/Sequential-logic-implementation-6-320.jpg)

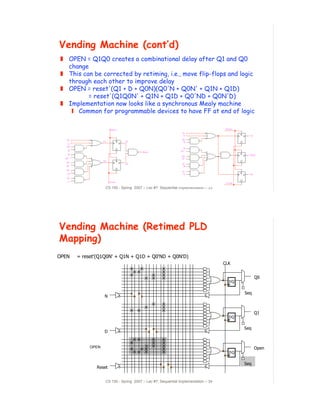

![Example: Vending Machine (cont’d)

! Suitable Abstract Representation

" Tabulate typical input sequences: Reset

# 3 nickels

# nickel, dime

S0

# dime, nickel

# two dimes N D

" Draw state diagram:

# Inputs: N, D, reset S1 S2

# Output: open chute N D N D

" Assumptions:

# Assume N and D asserted S4 S5 S6

S3

for one cycle [open] [open] [open]

# Each state has a self loop N

for N = D = 0 (no coin)

S7

[open]

CS 150 - Spring 2007 – Lec #7: Sequential Implementation – 17

Example: Vending Machine (cont’d)

! Minimize number of states - reuse states whenever possible

Reset present inputs next output

state D N state open

0¢ 0 0 0¢ 0

0 1 5¢ 0

0¢ 1 0 10¢ 0

1 1 – –

N 5¢ 0 0 5¢ 0

0 1 10¢ 0

5¢ D 1 0 15¢ 0

1 1 – –

N 10¢ 0 0 10¢ 0

0 1 15¢ 0

D 1 0 15¢ 0

10¢

1 1 – –

15¢ – – 15¢ 1

N+D

15¢ symbolic state table

[open]

CS 150 - Spring 2007 – Lec #7: Sequential Implementation – 18](https://image.slidesharecdn.com/sequentiallogicimplementation-130322091318-phpapp01/85/Sequential-logic-implementation-9-320.jpg)

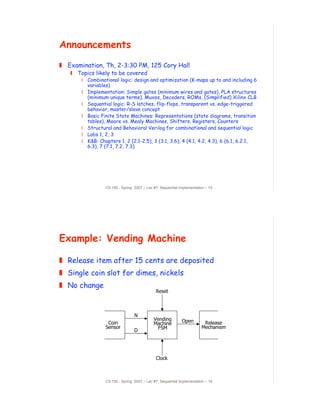

![Example: Vending Machine (cont’d)

! One-hot Encoding

present state inputs next state output

Q3 Q2 Q1 Q0 D N D3 D2 D1 D0 open

0 0 0 1 0 0 0 0 0 1 0 D0 = Q0 D’ N’

0 1 0 0 1 0 0

1 0 0 1 0 0 0

1 1 - - - - - D1 = Q0 N + Q1 D’ N’

0 0 1 0 0 0 0 0 1 0 0

0 1 0 1 0 0 0 D2 = Q0 D + Q1 N + Q2 D’ N’

1 0 1 0 0 0 0

1 1 - - - - -

0 1 0 0 0 0 0 1 0 0 0 D3 = Q1 D + Q2 D + Q2 N + Q3

0 1 1 0 0 0 0

1 0 1 0 0 0 0 OPEN = Q3

1 1 - - - - -

1 0 0 0 - - 1 0 0 0 1

CS 150 - Spring 2007 – Lec #7: Sequential Implementation – 21

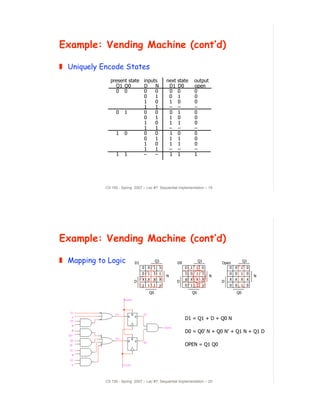

Equivalent Mealy and Moore State

Diagrams

! Moore machine Mealy machine

" outputs associated with state outputs associated with transitions

Reset N’ D’ + Reset Reset/0 (N’ D’ + Reset)/0

0¢

N’ D’ 0¢ N’ D’/0

[0]

N N/0

D 5¢ D/0

N’ D’ 5¢ N’ D’/0

[0]

N N/0

10¢

D N’ D’ D/1 10¢ N’ D’/0

[0]

N+D N+D/1

15¢

Reset’ 15¢ Reset’/1

[1]

CS 150 - Spring 2007 – Lec #7: Sequential Implementation – 22](https://image.slidesharecdn.com/sequentiallogicimplementation-130322091318-phpapp01/85/Sequential-logic-implementation-11-320.jpg)

![Moore Verilog FSM for Vending Machine

module vending (open, Clk, Reset, N, D);

input Clk, Reset, N, D; output open; N’ D’ + Reset

reg open; reg state; // state register Reset

reg next_state;

parameter zero = 0, five = 1, ten = 2, fifteen = 3;

0¢

N’ D’

always @(N or D or state) [0]

case (state)

zero: begin N

if (D) next_state = five;

D 5¢

else if (N) next_state = ten; N’ D’

else next_state = zero; [0]

open = 0;

N

end

… 10¢

fifteen: begin D N’ D’

[0]

if (!Reset) next_state = fifteen;

else next_state = zero; N+D

open = 1;

end 15¢

endcase Reset’

[1]

always @(posedge clk)

if (Reset || (!N && !D)) state <= zero;

else state <= next_state;

endmodule

CS 150 - Spring 2007 – Lec #7: Sequential Implementation – 23

7

Mealy Verilog FSM for Vending Machine

module vending (open, Clk, Reset, N, D);

input Clk, Reset, N, D; output open;

Reset/0 (N’ D’ + Reset)/0

reg open; reg state; // state register

reg next_state; reg next_open;

parameter zero = 0, five = 1, ten = 2, fifteen = 3;

0¢ N’ D’/0

always @(N or D or state)

case (state)

N/0

zero: begin

if (D) begin

D/0 5¢ N’ D’/0

next_state = ten; next_open = 0;

end

else if (N) begin N/0

next_state = five; next_open = 0;

end

else begin D/1 10¢ N’ D’/0

next_state = zero; next_open = 0;

end N+D/1

end

…

15¢ Reset’/1

endcase

always @(posedge clk)

if (Reset || (!N && !D)) begin state <= zero; open <= 0; end

else begin state <= next_state; open <= next_open; end

endmodule

CS 150 - Spring 2007 – Lec #7: Sequential Implementation – 24

7](https://image.slidesharecdn.com/sequentiallogicimplementation-130322091318-phpapp01/85/Sequential-logic-implementation-12-320.jpg)