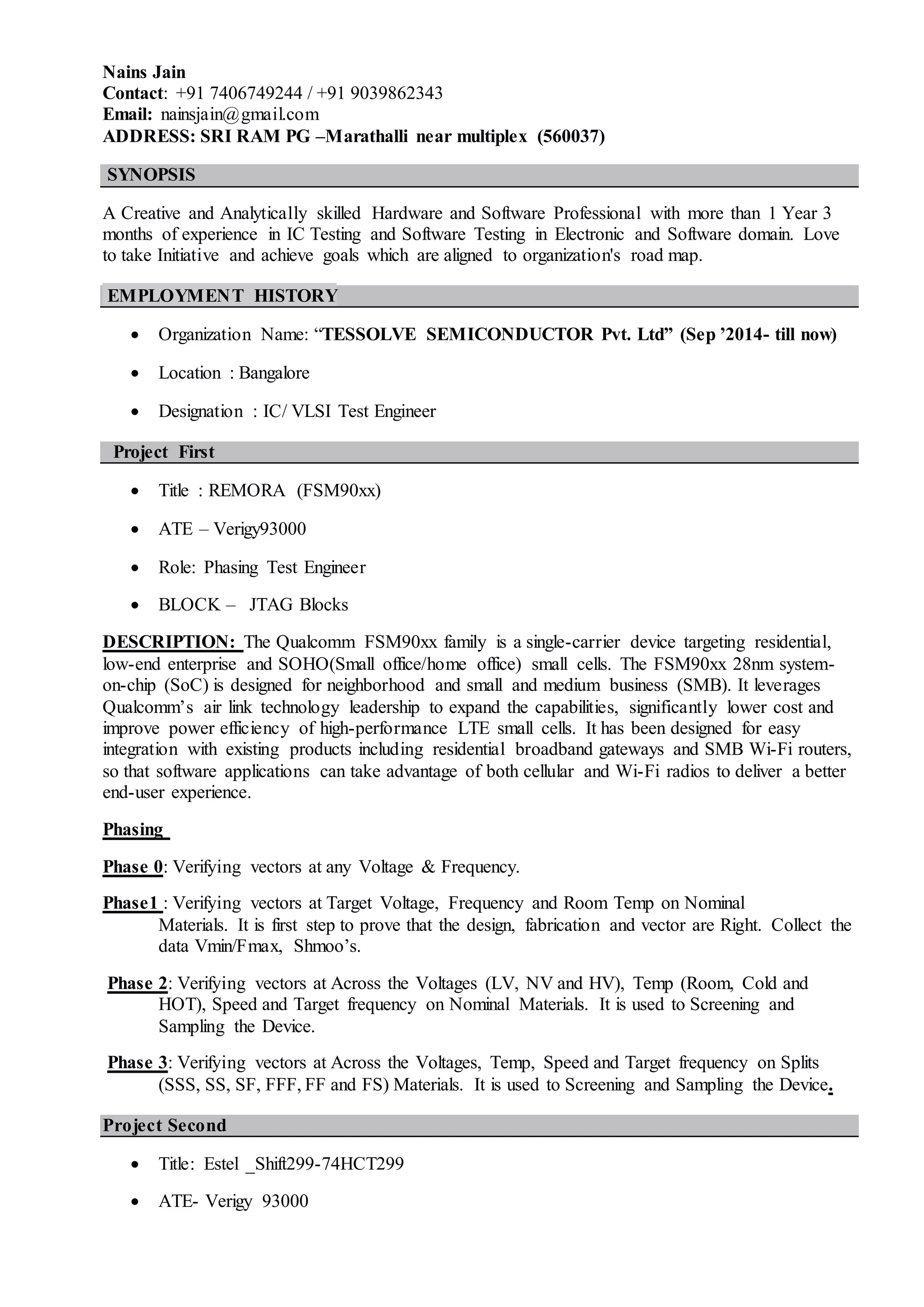

Nains Jain has over 1 year and 3 months of experience as an IC/VLSI Test Engineer and Manual Test Engineer. He has worked on projects involving IC testing for Qualcomm's FSM90xx family of chips and shift register testing. His responsibilities included test program creation, functional testing, debugging, and result analysis. He is proficient in automation testing tools like Verigy 93000 and Smartest as well as manual testing methodologies. He has a Bachelor's degree in Electronics and Communication Engineering.