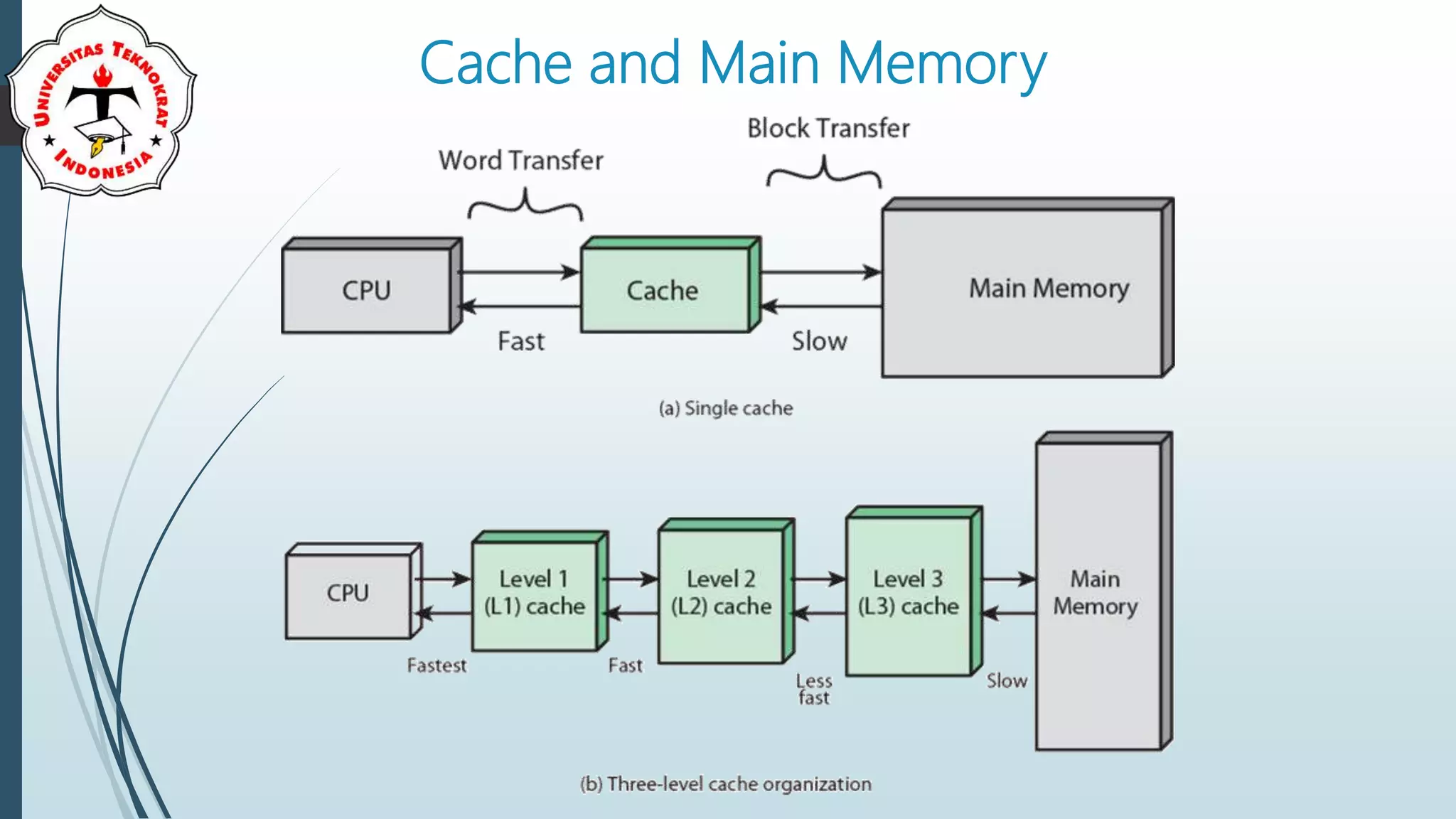

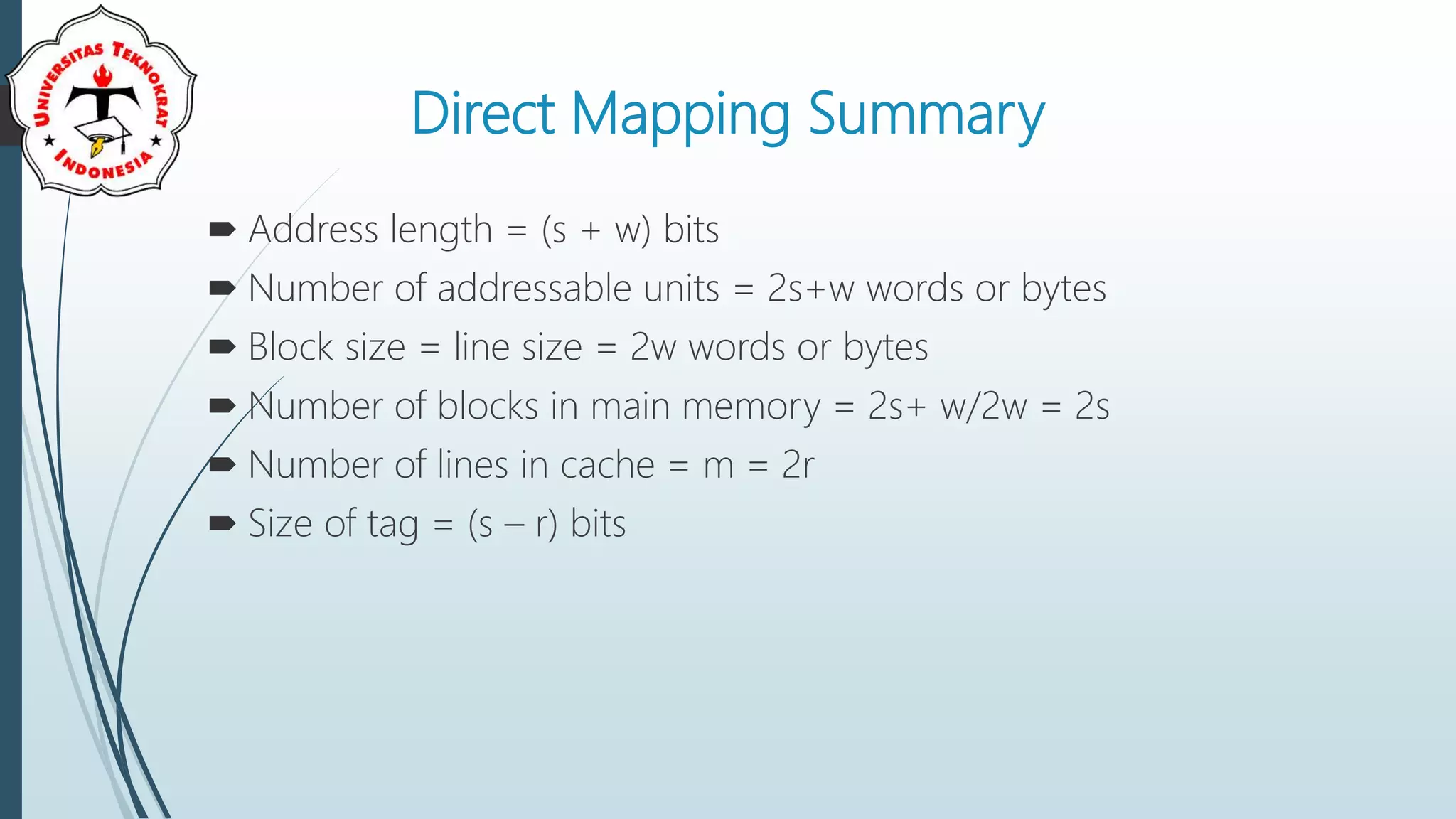

Dokumen tersebut membahas tentang memori komputer khususnya cache memory. Cache memory merupakan memori cepat yang berfungsi menyimpan data dan instruksi yang sering diakses untuk mempercepat akses prosesor. Dokumen menjelaskan definisi, cara kerja, desain, dan jenis-jenis cache memory seperti direct mapping, associative mapping, serta perbandingan antara cache dengan memori utama.