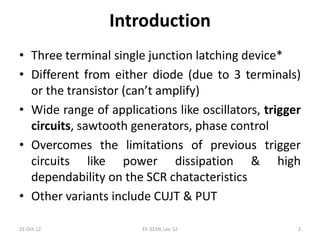

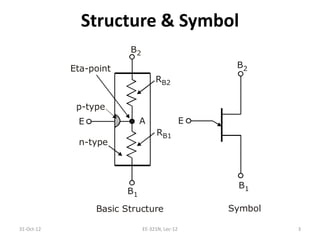

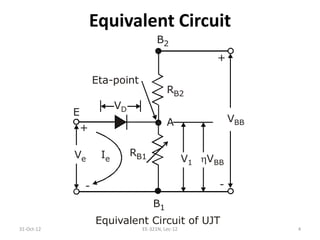

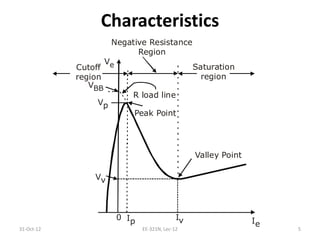

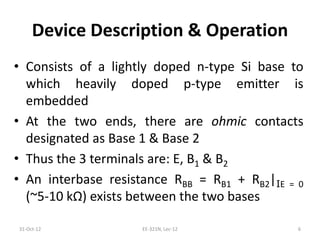

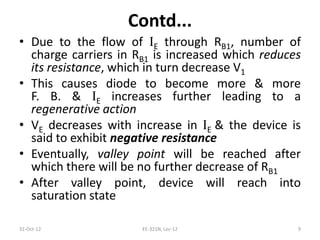

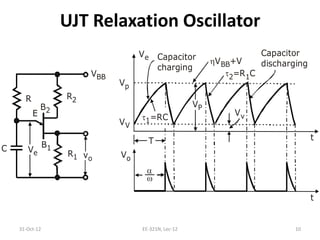

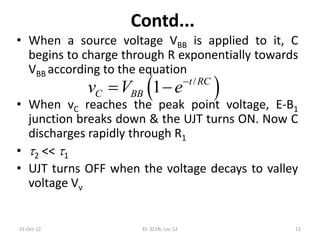

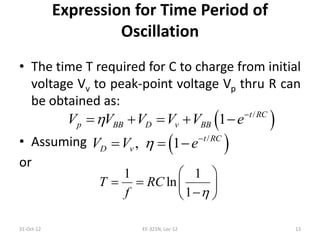

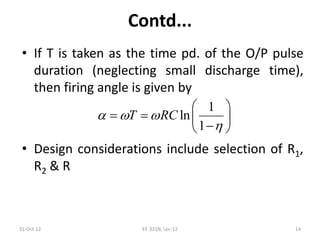

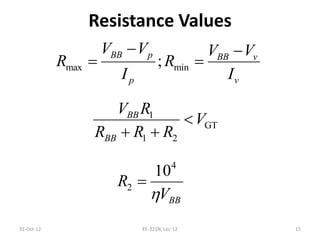

The document provides an overview of the Unijunction Transistor (UJT), describing its unique three-terminal structure and various applications including trigger circuits and oscillators. It explains the device's characteristics, operation, and how it can exhibit negative resistance, which is utilized in relaxation oscillators. Additionally, it includes information on circuit configurations, charging and discharging processes, and key parameters for design considerations.