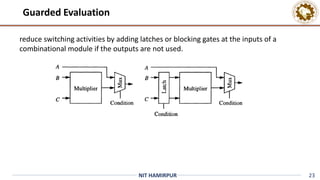

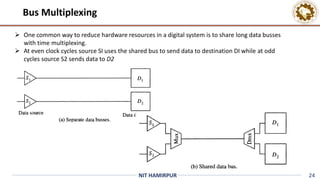

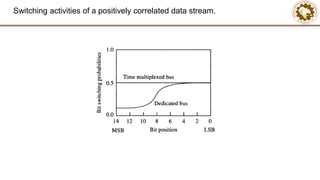

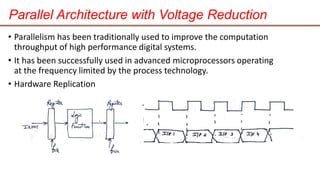

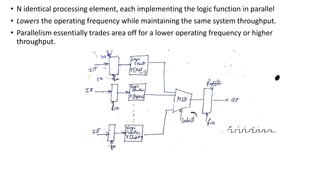

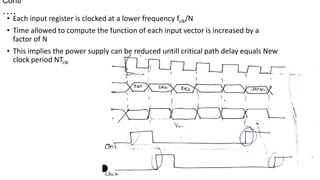

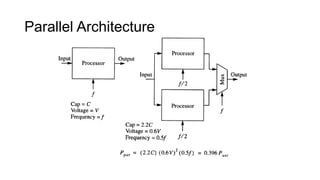

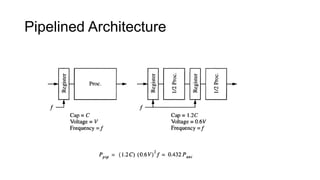

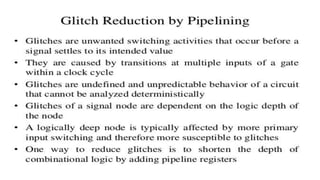

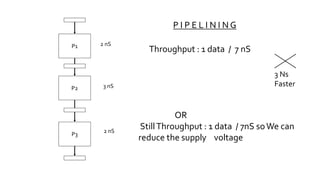

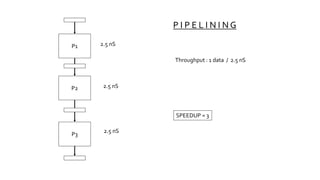

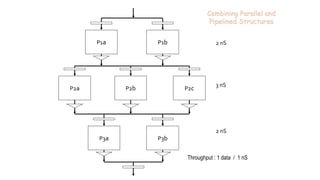

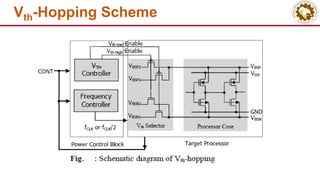

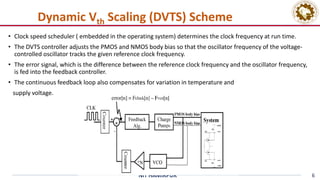

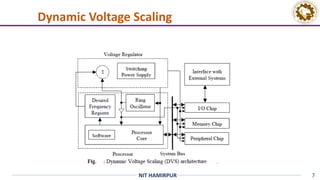

The document provides an overview of various low power VLSI design techniques at the architectural level. It discusses dynamic voltage scaling, dynamic threshold voltage schemes like Vth-hopping and dynamic Vth scaling, microprocessor sleep modes, adaptive filtering, switching activity reduction using guarded evaluation, bus multiplexing, and parallel and pipelined architectures. It explains how these techniques can be used to reduce power consumption by decreasing voltage/frequency, turning off unused components, reducing switching activity, and improving throughput without increasing frequency.

![21

NIT HAMIRPUR

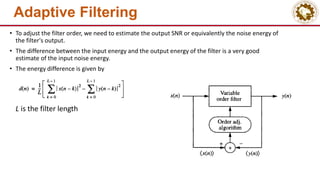

Adaptive Filtering

• The actual noise energy of the output can be estimated by

ESB [Order(n)] is the stop-band energy of the filter and α is a constant.

The energy ESB [Order(n)] can be obtained by taking the integration of the filter transfer

function at the stop-band and stored in a lookup table.

Q(n) represents the noise energy measured at a particular

output sample n. The filter order update algorithm is](https://image.slidesharecdn.com/architecturalleveltechniques-210517113456/85/Architectural-Level-Techniques-21-320.jpg)