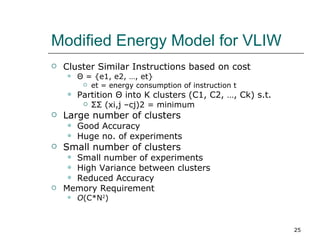

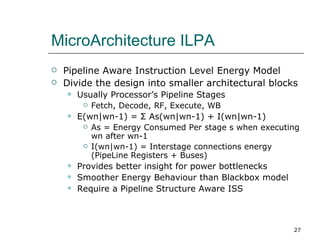

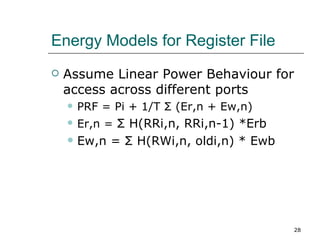

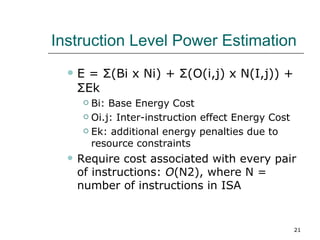

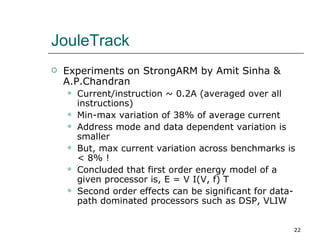

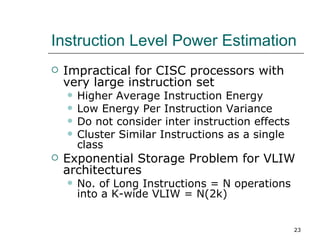

This document discusses instruction level power analysis (ILPA) for estimating processor power consumption. It describes how ILPA works by associating an energy cost with each instruction based on its operations and accounting for inter-instruction effects. Initially used for RISC processors, ILPA methods were modified for VLIW/EPIC processors by considering independent energy dissipation across execution slots and clustering similar instructions. ILPA does not provide insight into core power consumption causes but was expanded to microarchitecture-aware models accounting for individual pipeline stages. Register files and caches can also be modeled based on access patterns and state transitions between cycles.

![Modified Energy Model for VLIW

Assume Independent Energy dissipation for

different Execution slots

Consider nop as the base energy

E(W) = ΣU(wn|wn-1) + mxpxS + lxqxM

U(wn|wn-1) = U(0|0) + Σv(wnk,wn-1k)

Wnk = operation issued on lane k by instruction wn

Example

Wn = [ ALU NOP NOP NOP], Wn-1 = [ LS NOP ALU

NOP]

U(wn|wn-1) = U(0|0) + v(ALU|LS) + v(NOP|ALU)

Memory Requirement

O(K*N2)

24](https://image.slidesharecdn.com/instructionlevelpoweranalysis-120602013341-phpapp02/85/Instruction-level-power-analysis-24-320.jpg)