More Related Content

PPTX

PDF

Microservices monitoring challange PDF

Telecoms Research Agenda 2011 PDF

itSMF Espana presentation DOC

PDF

PDF

PDF

Lessons learned to keep cholesterol on proper level base on private cloud pr... Featured

PDF

2024 Trend Updates: What Really Works In SEO & Content Marketing PDF

Storytelling For The Web: Integrate Storytelling in your Design Process PDF

Artificial Intelligence, Data and Competition – SCHREPEL – June 2024 OECD dis... PDF

How to Leverage AI to Boost Employee Wellness - Lydia Di Francesco - SocialHR... PDF

2024 State of Marketing Report – by Hubspot PDF

Everything You Need To Know About ChatGPT PDF

Product Design Trends in 2024 | Teenage Engineerings PDF

How Race, Age and Gender Shape Attitudes Towards Mental Health PDF

AI Trends in Creative Operations 2024 by Artwork Flow.pdf PDF

PDF

PEPSICO Presentation to CAGNY Conference Feb 2024 PDF

Content Methodology: A Best Practices Report (Webinar) PPTX

How to Prepare For a Successful Job Search for 2024 PDF

Social Media Marketing Trends 2024 // The Global Indie Insights PDF

Trends In Paid Search: Navigating The Digital Landscape In 2024 PDF

5 Public speaking tips from TED - Visualized summary PDF

ChatGPT and the Future of Work - Clark Boyd PDF

Getting into the tech field. what next PDF

Google's Just Not That Into You: Understanding Core Updates & Search Intent PDF

How to have difficult conversations 85 87

- 1.

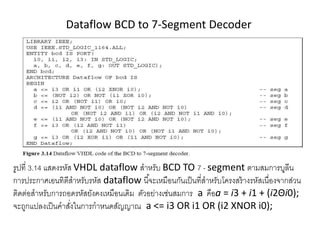

Dataflow BCD to7-Segment Decoder

รูปที่ 3.14 แสดงรหัส VHDL dataflow สำหรับ BCD TO 7 - segment ตำมสมกำรบูลีน

กำรประกำศเอนทิตีสำหรับรหัส dataflow นี้จะเหมือนกันเป็นที่สำหรับโครงสร้ำงรหัสเนื่องจำกส่วน

ติดต่อสำหรับกำรถอดรหัสยังคงเหมือนเดิม ตัวอย่ำงเช่นสมกำร a คือa = i3 + i1 + (i2Θi0);

จะถูกแปลงเป็นคำสั่งในกำรกำหนดสัญญำณ a <= i3 OR i1 OR (i2 XNOR i0);

- 3.

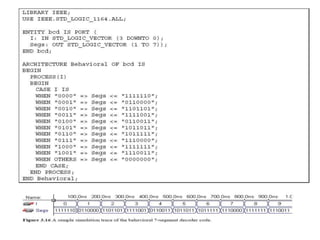

3.7.3 Behavioral BCDto 7-Segment Decoder

กำรประกำศเอนทิตี้แตกต่ำงกันเล็กน้อยจำกกำรเขียนแบบ Dataflow คือ

สัญญำณ i0, i1, i2, i3 และเรำได้ประกำศเวกเตอร์เป็น

STD_LOGIC_VECTOR นั่นคือเวกเตอร์ของชนิด STD_LOGIC ควำมยำว

ของเวกเตอร์จะถูกระบุโดยช่วง (3DOWNTO 0) หมำยเลขแรก (3) ในช่วงหมำยถึง

ดัชนีของบิตที่สำคัญที่สุดของเวกเตอร์และตัวเลขที่สอง (0) ในช่วงหมำยถึงดัชนีของบิต

อย่ำงมีนัยสำคัญน้อยของเวกเตอร์ ในทำนองเดียวกันเจ็ดเอำต์พุต สัญญำณไปจะถูก

แทนที่ด้วย Segs STD_LOGIC_VECTOR จำก 7 บิต