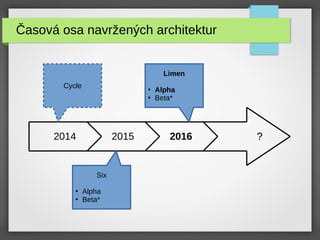

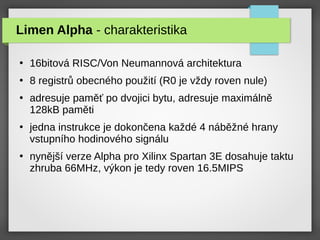

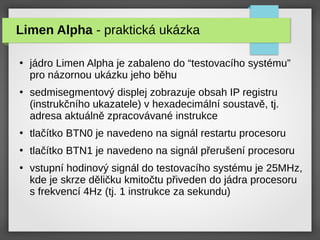

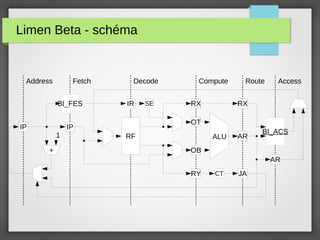

Představení mého prvního uceleného procesoru Limen z roku 2016 v rámci obhajoby maturitní práce na SŠIEŘ Rožnov pod Radhoštěm. Tento procesor dal později vzniknout mému prvnímu dvoujádrovému procesoru Limen Alpha. Procesor byl popsán v jazyce VHDL.

Zdrojový kód Limen: https://github.com/dominiksalvet/limen

Text maturitní práce: https://is.muni.cz/publication/1491040/en