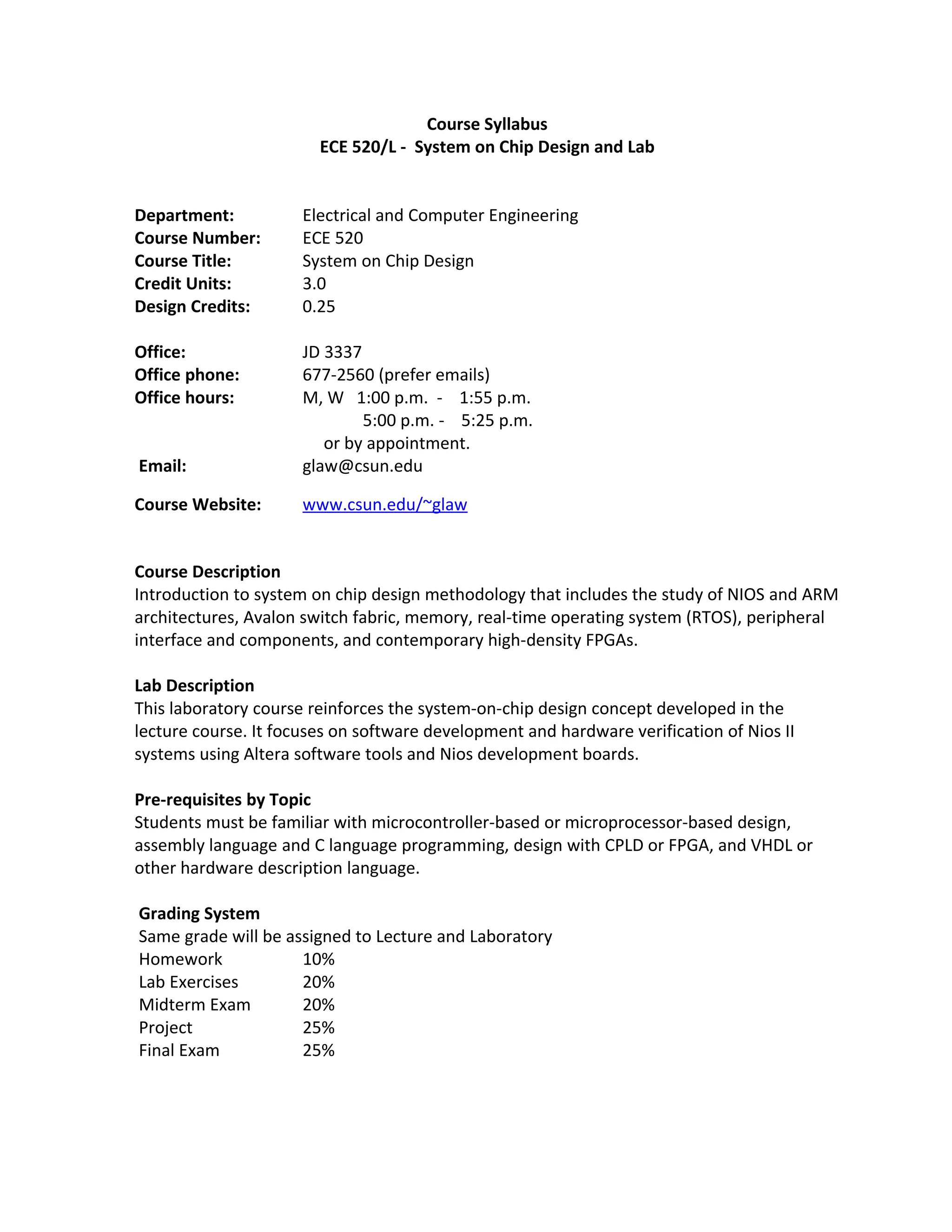

This document outlines the syllabus for the ECE 520/L System on Chip Design course and lab. The course introduces students to system on chip design methodology using NIOS and ARM architectures on Altera FPGAs. The lab portion reinforces these concepts through software and hardware design projects using NIOS development boards. Students are evaluated based on homework, lab exercises, exams, a design project, and lab participation. Upon completing the course, students should understand soft-core processor design, peripheral interfaces, and SOC implementation on FPGAs.