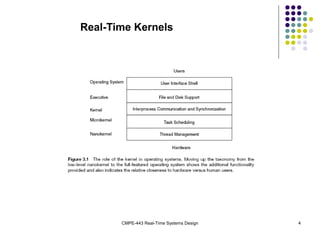

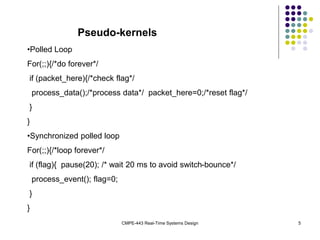

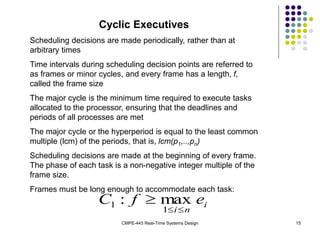

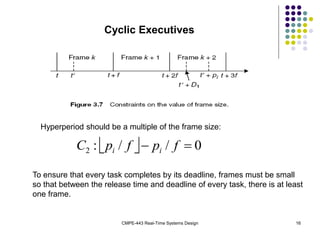

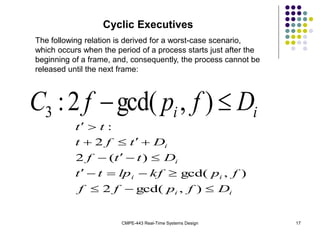

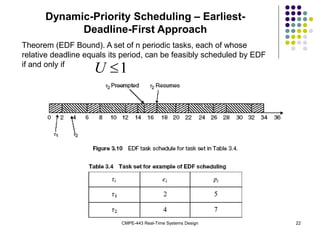

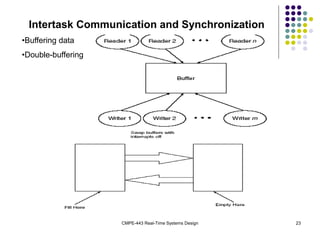

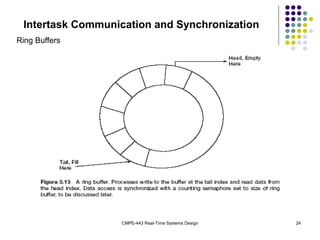

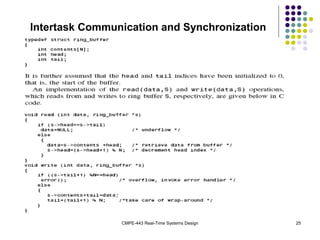

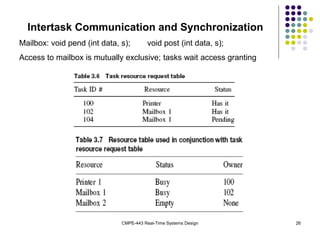

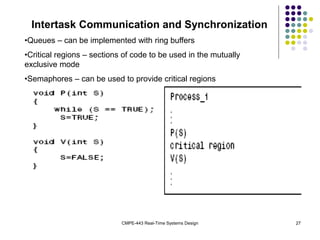

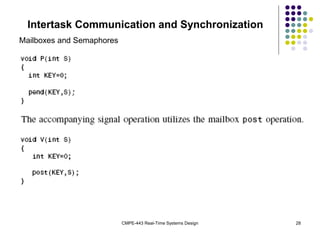

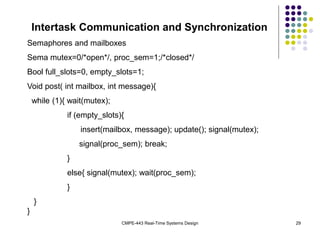

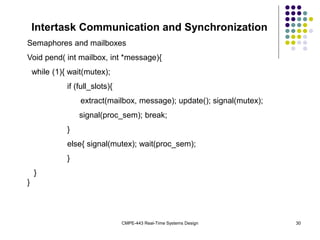

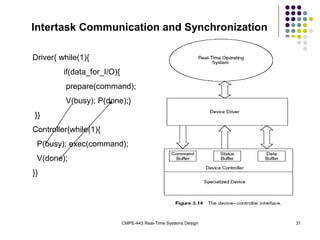

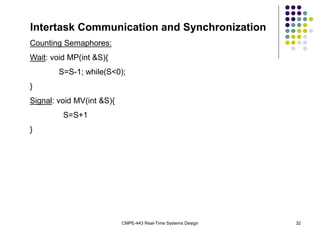

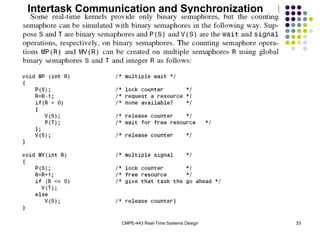

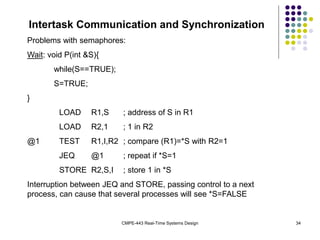

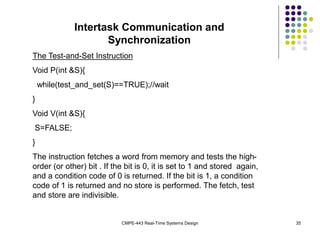

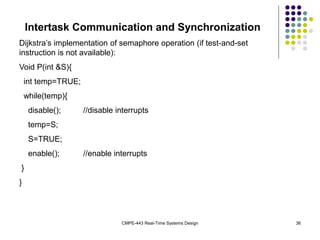

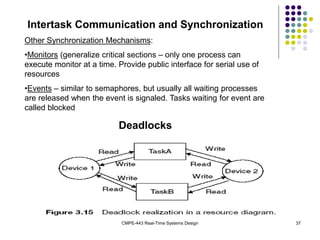

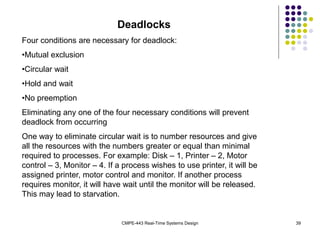

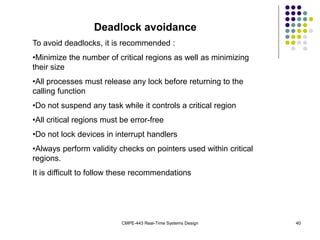

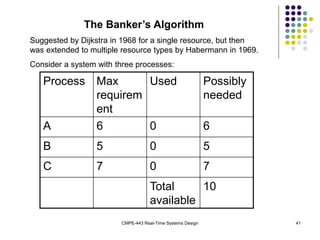

This document provides an overview of real-time operating systems and kernel concepts across 34 slides. The key topics covered include real-time kernels, tasks and processes, scheduling algorithms like priority-based and cyclic executives, intertask communication methods like mailboxes and semaphores, and synchronization techniques.