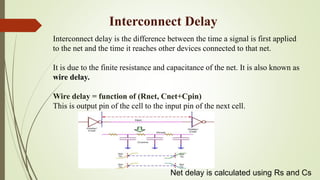

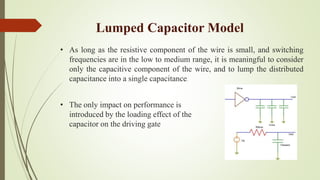

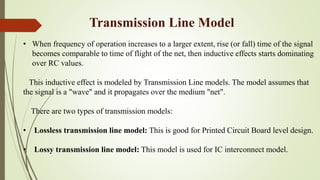

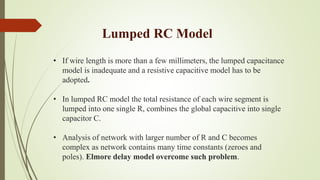

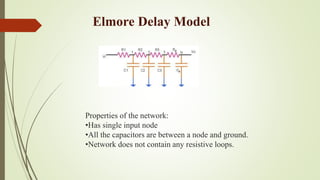

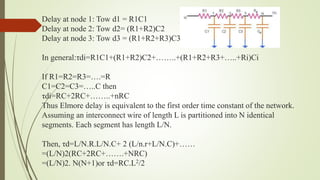

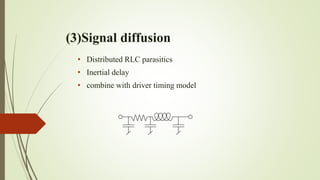

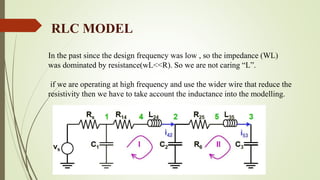

This document discusses different interconnect timing models used to model delays caused by interconnects in integrated circuits. It describes lumped capacitor, transmission line, lumped RC, Elmore delay, distributed RC, and RLC models. The lumped capacitor and transmission line models treat interconnects as either purely capacitive or propagating waves, while the lumped RC, distributed RC, and RLC models account for resistive and inductive effects at higher frequencies. The Elmore delay model provides a simplified yet accurate way to calculate delays in RC networks. Overall, the choice of timing model depends on factors like the operating frequency and interconnect geometry.