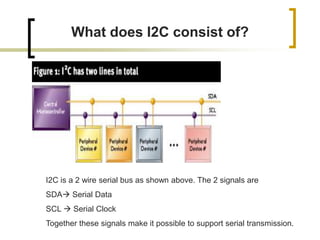

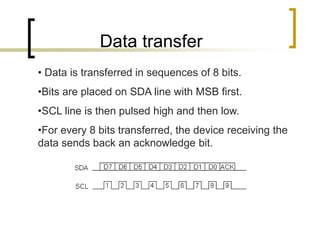

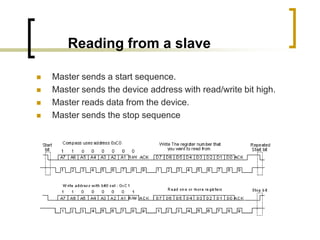

I2C is a serial communication protocol used to connect integrated circuits. It was developed by Philips in the 1980s and uses just two bidirectional lines - serial data line (SDA) and serial clock line (SCL). I2C has endured because it provides reliable communication using software-controlled collision detection at transfer rates up to 3.4 Mbps. Data is transferred between a master device that initiates the transaction and slave devices with unique addresses in sequences of 8-bit bytes with acknowledgement.