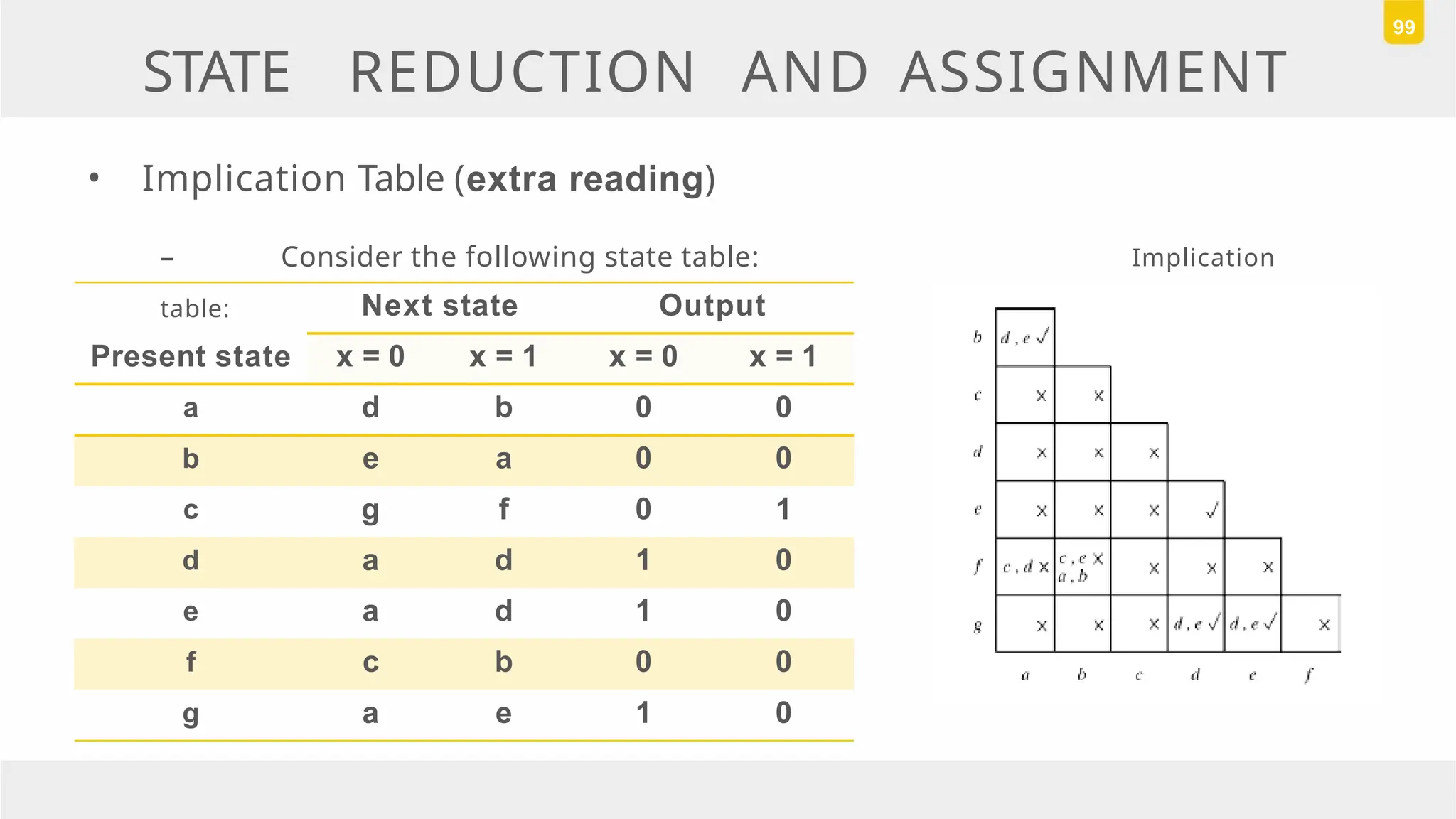

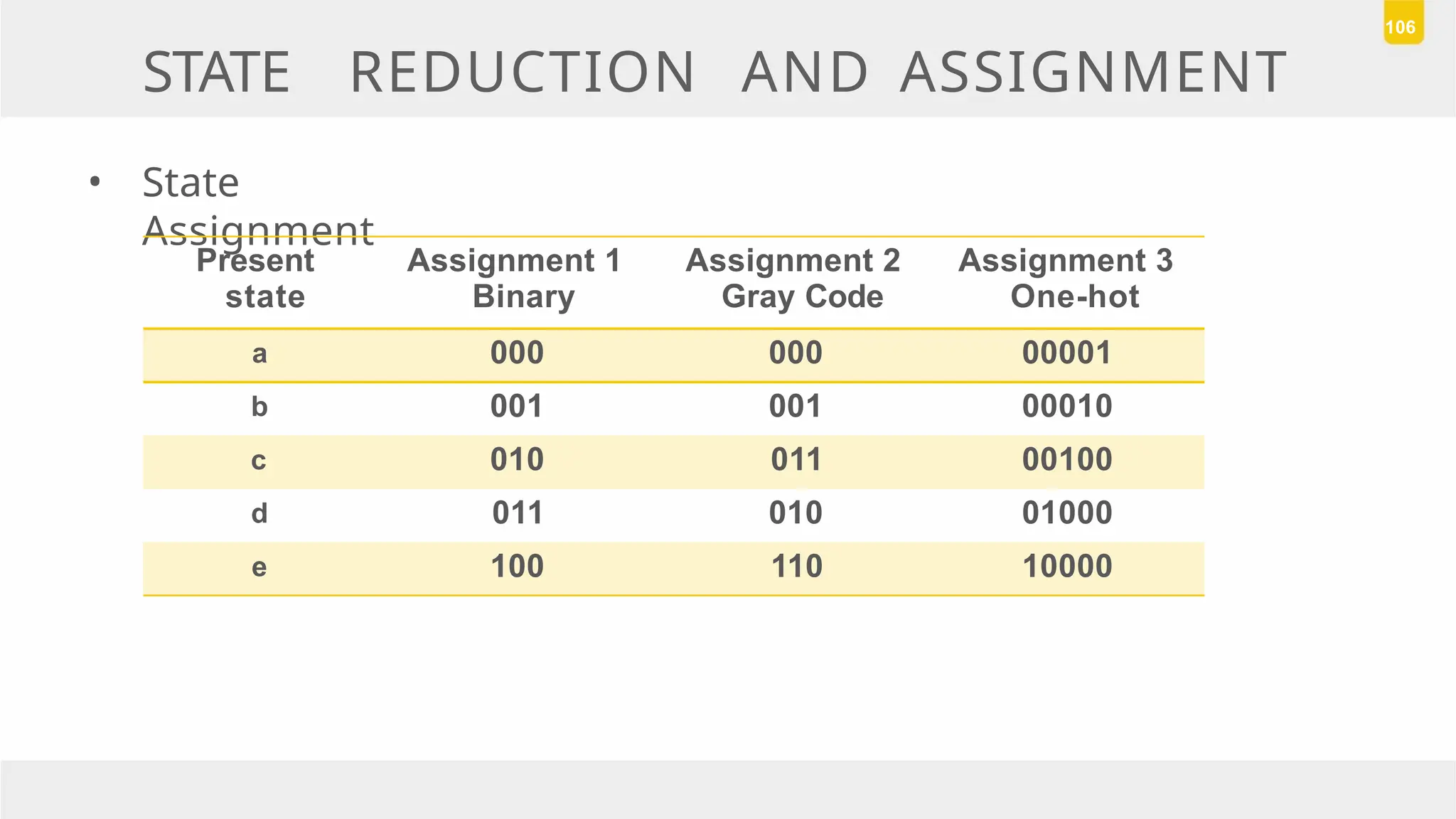

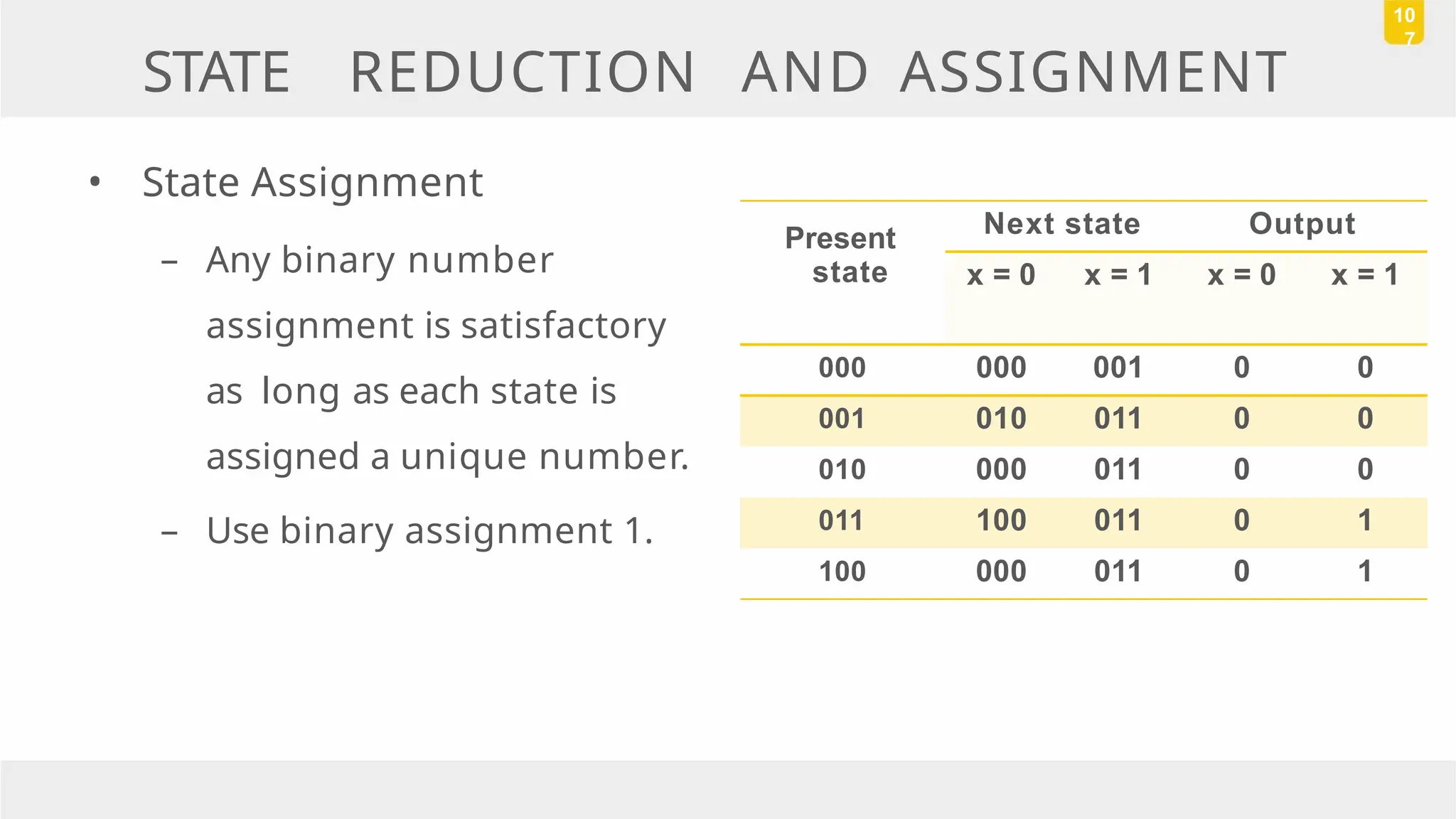

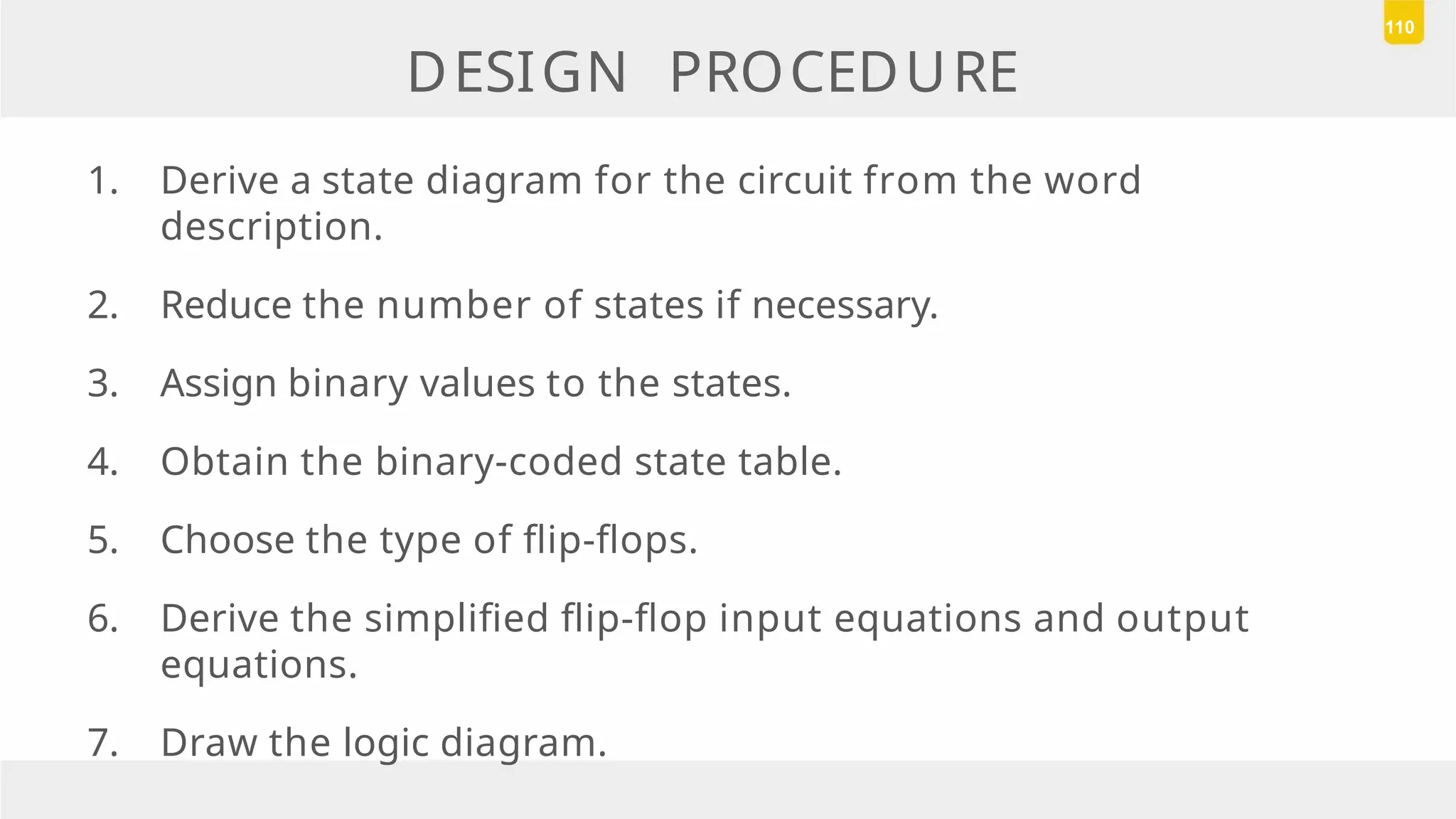

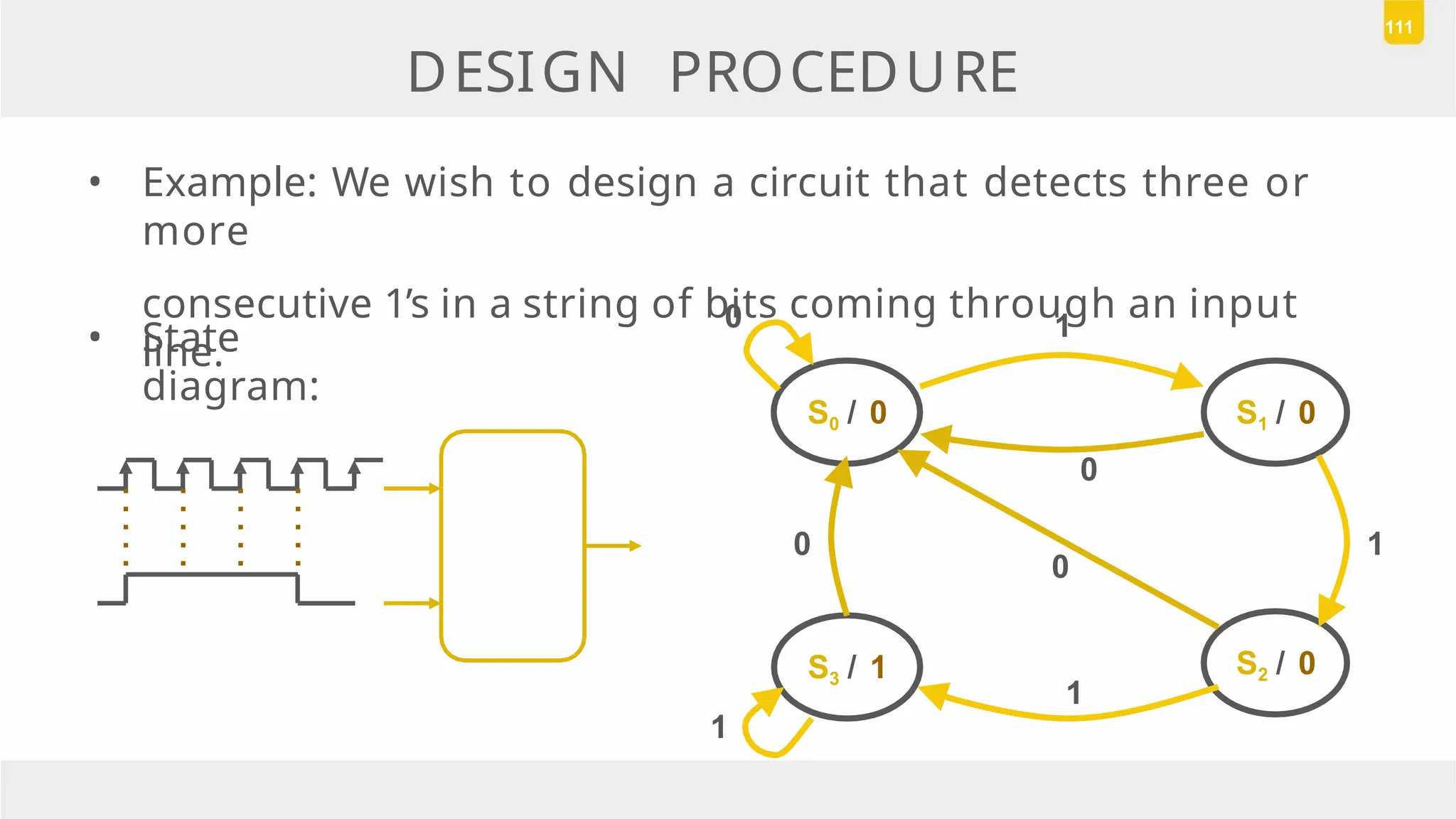

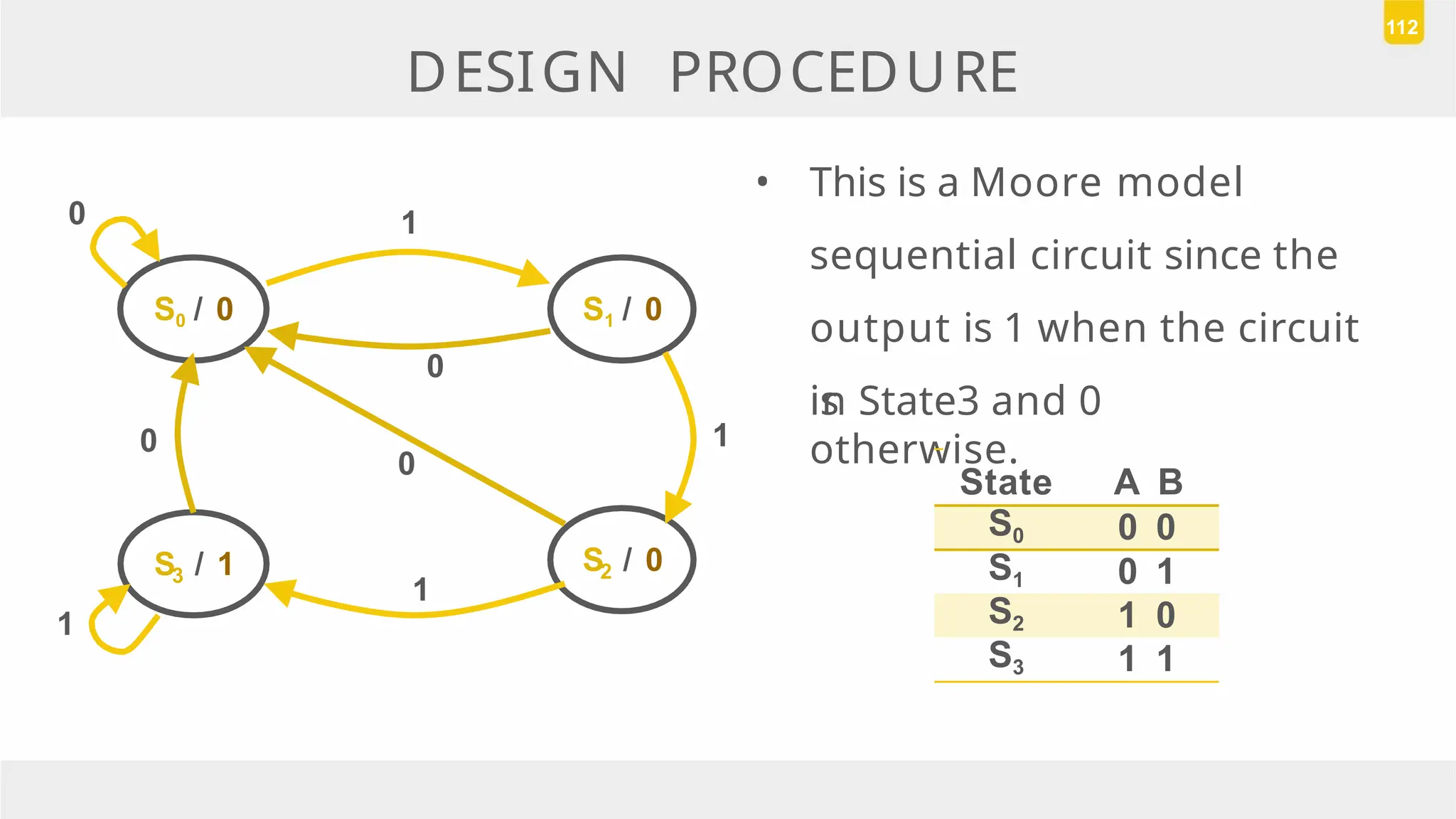

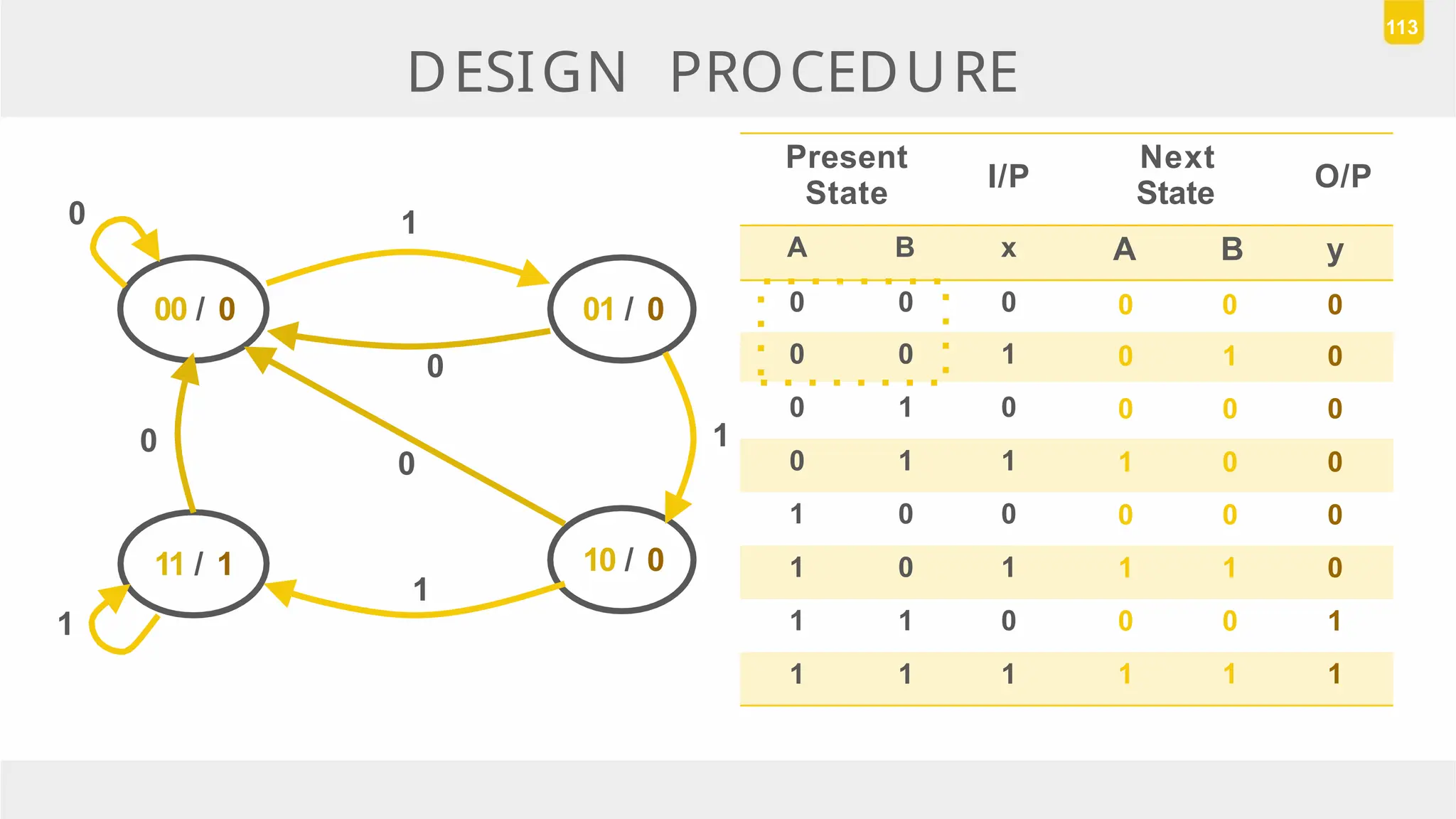

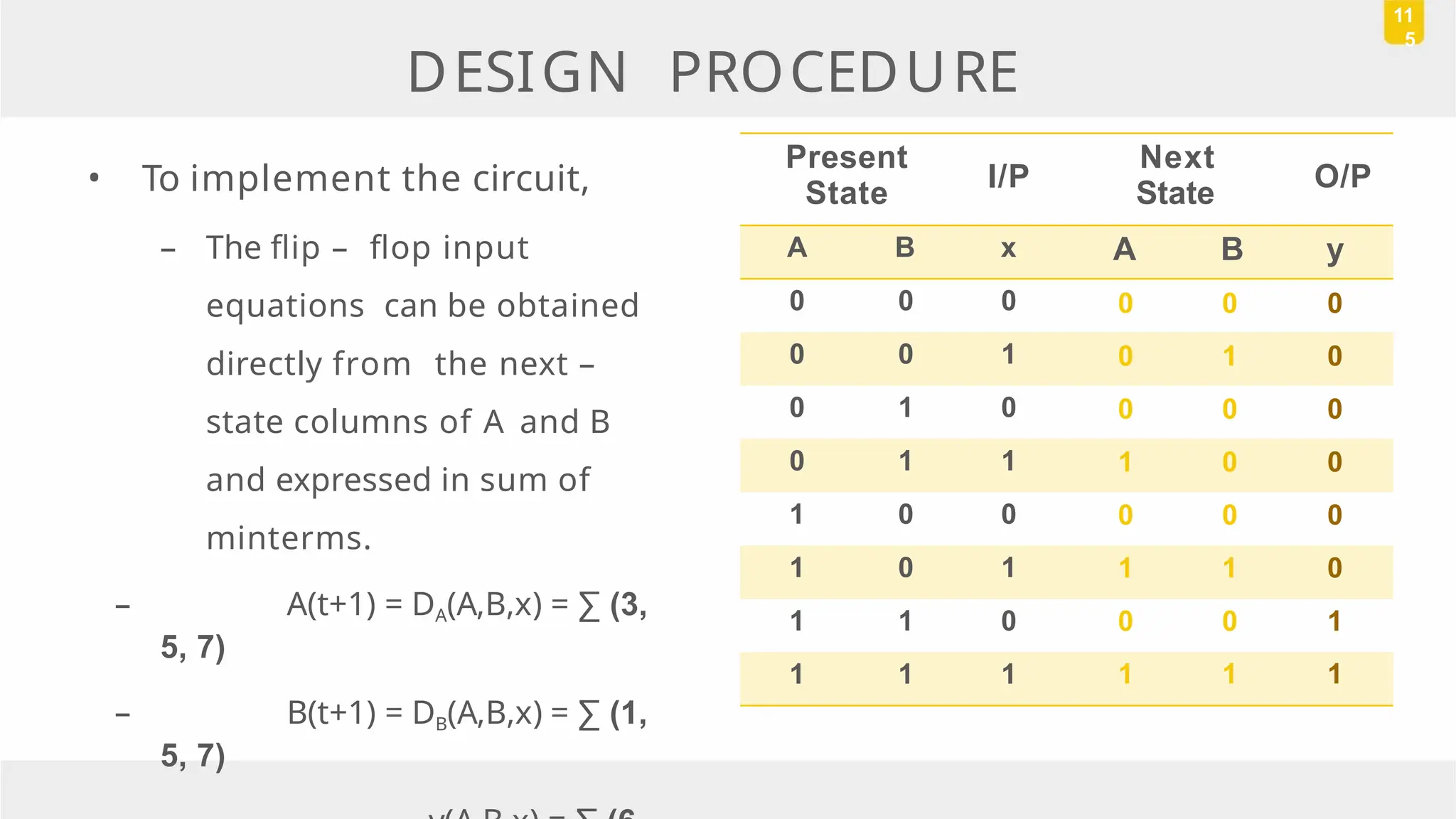

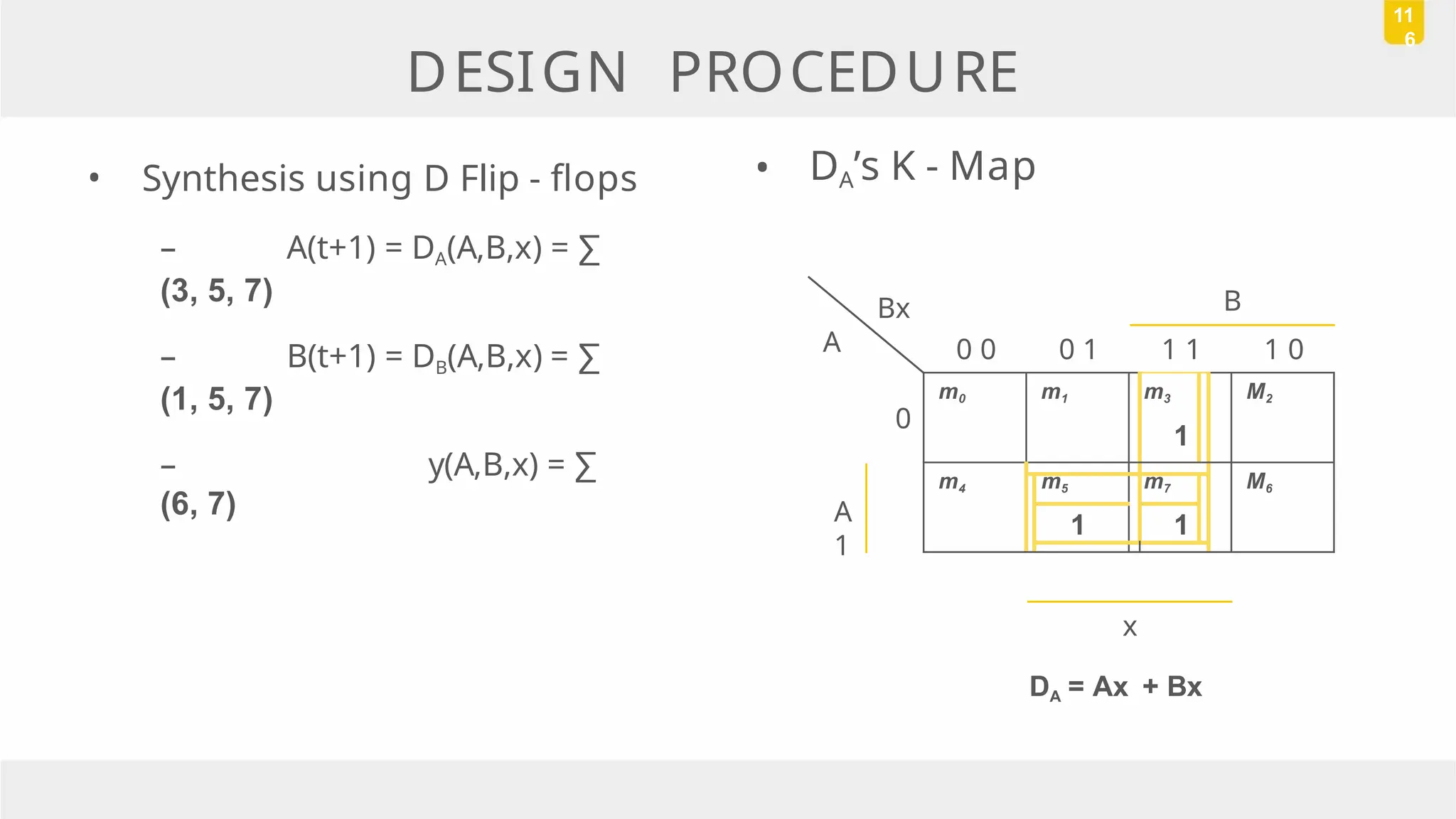

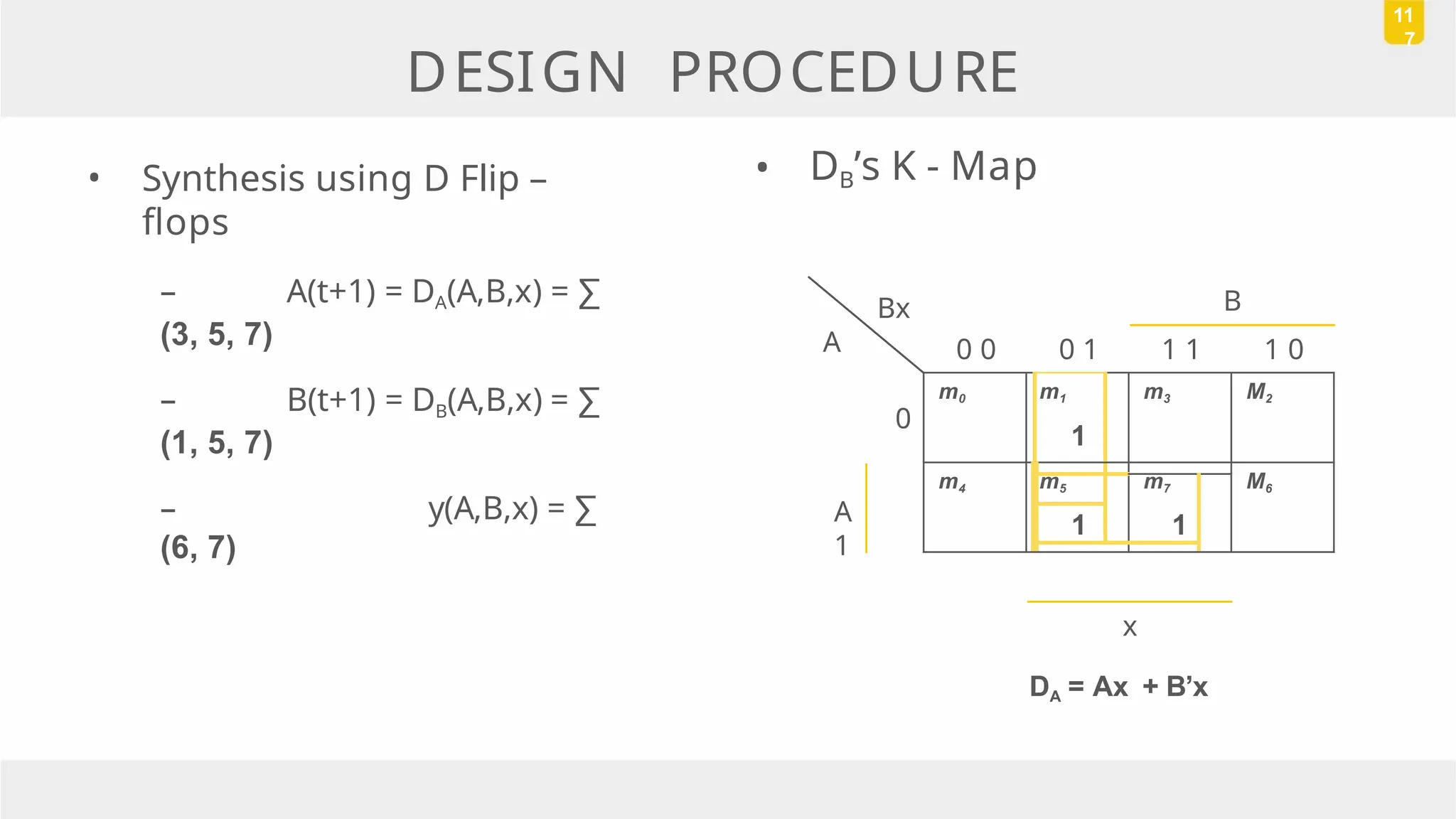

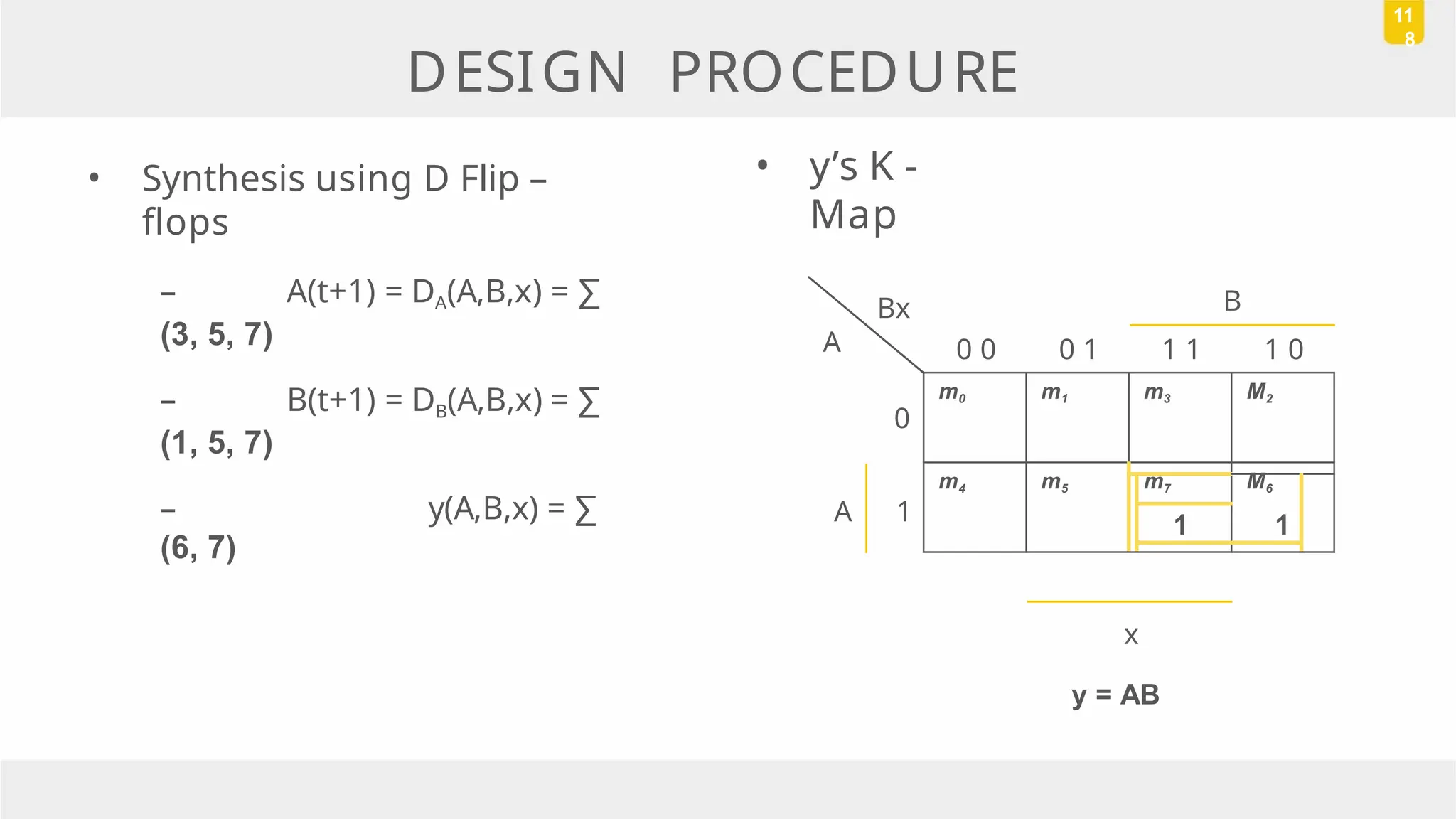

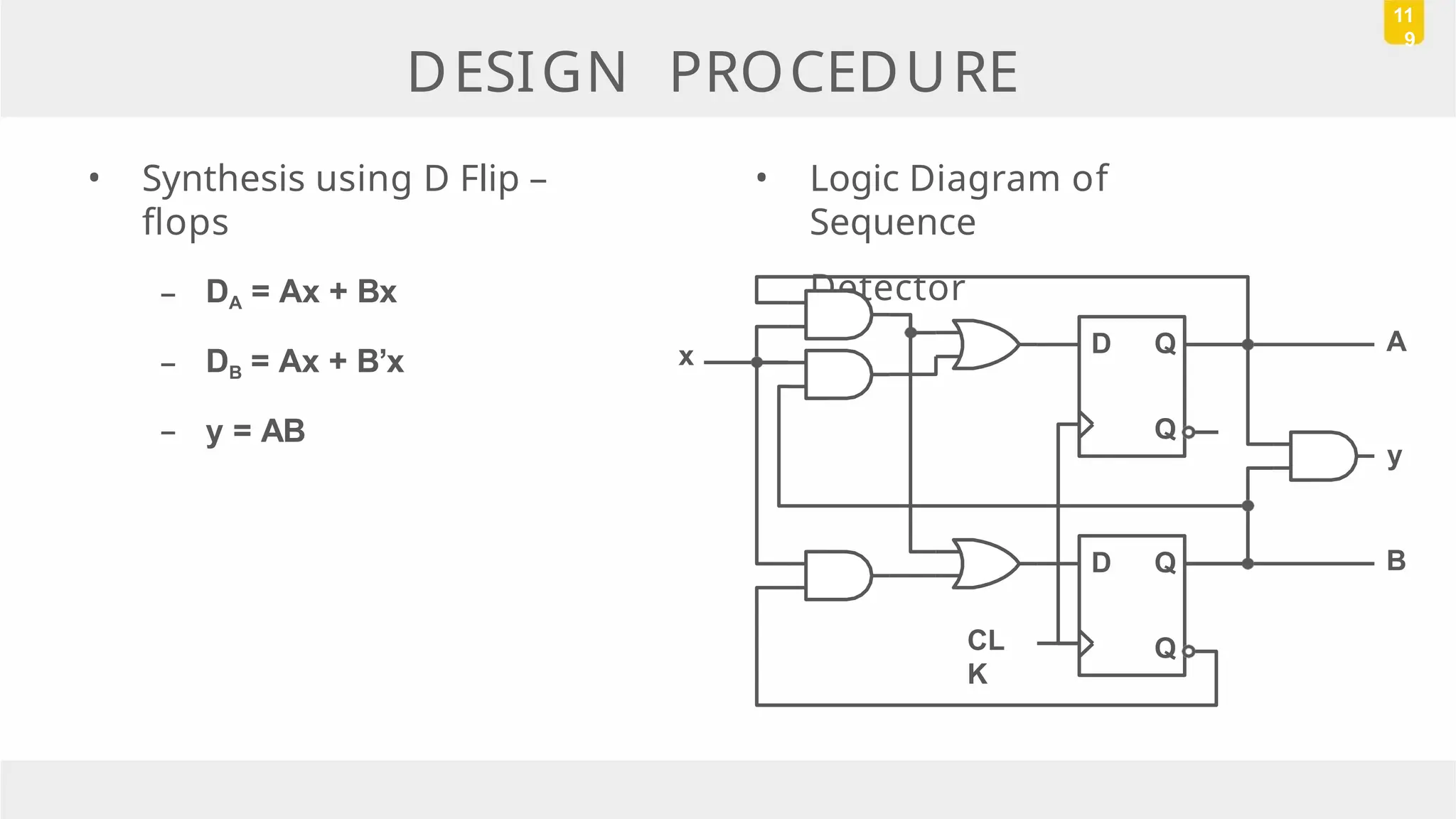

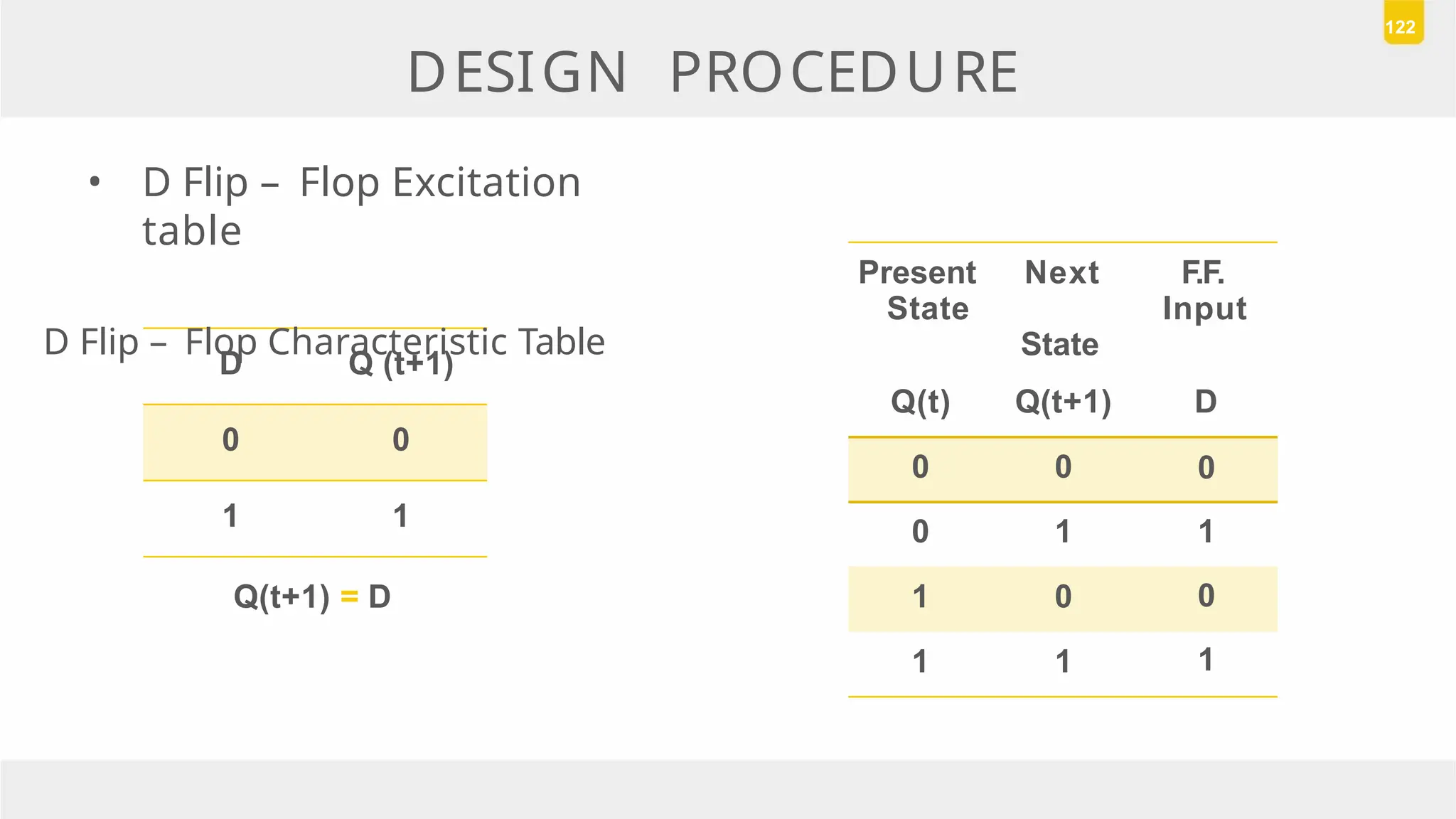

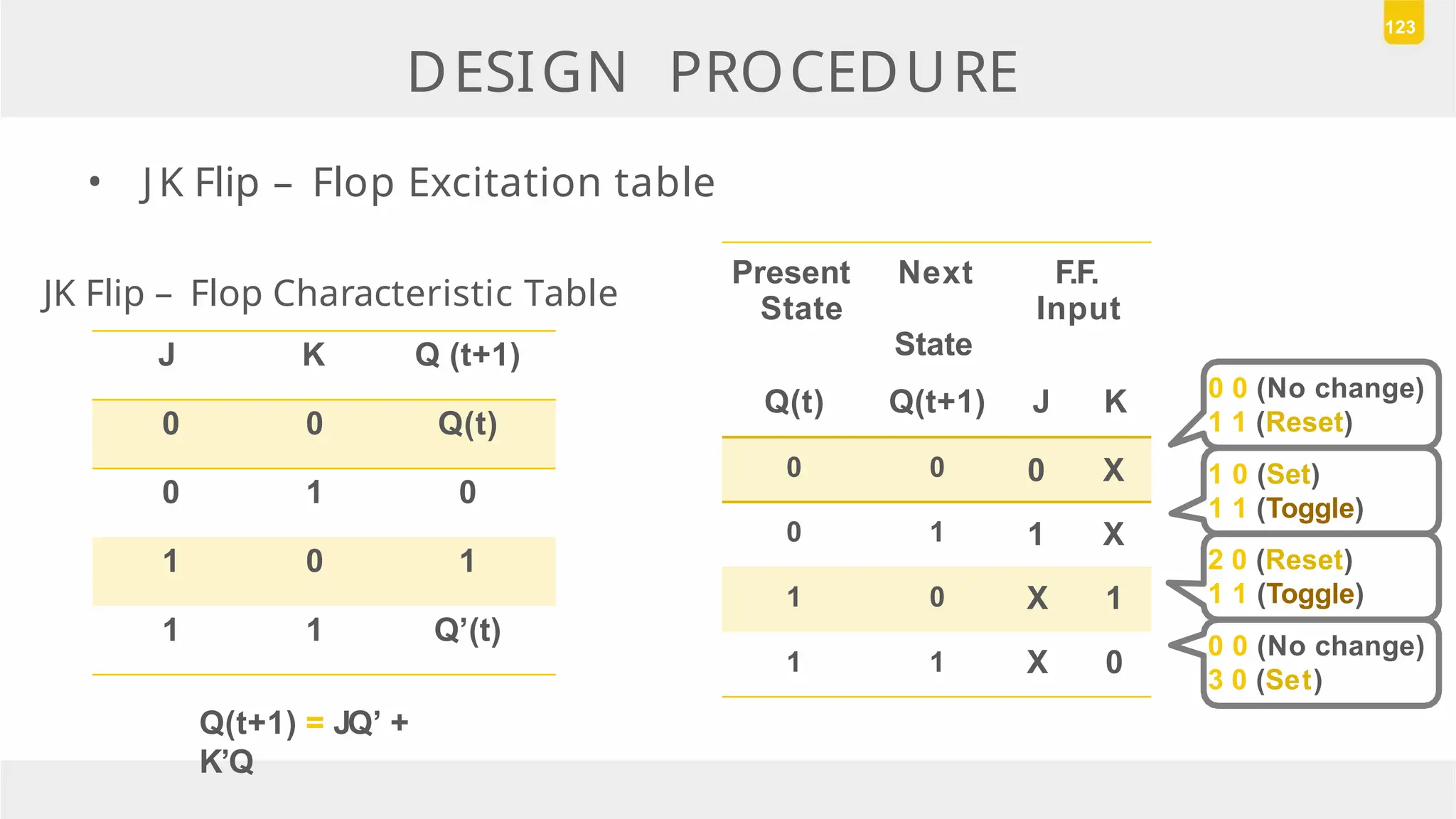

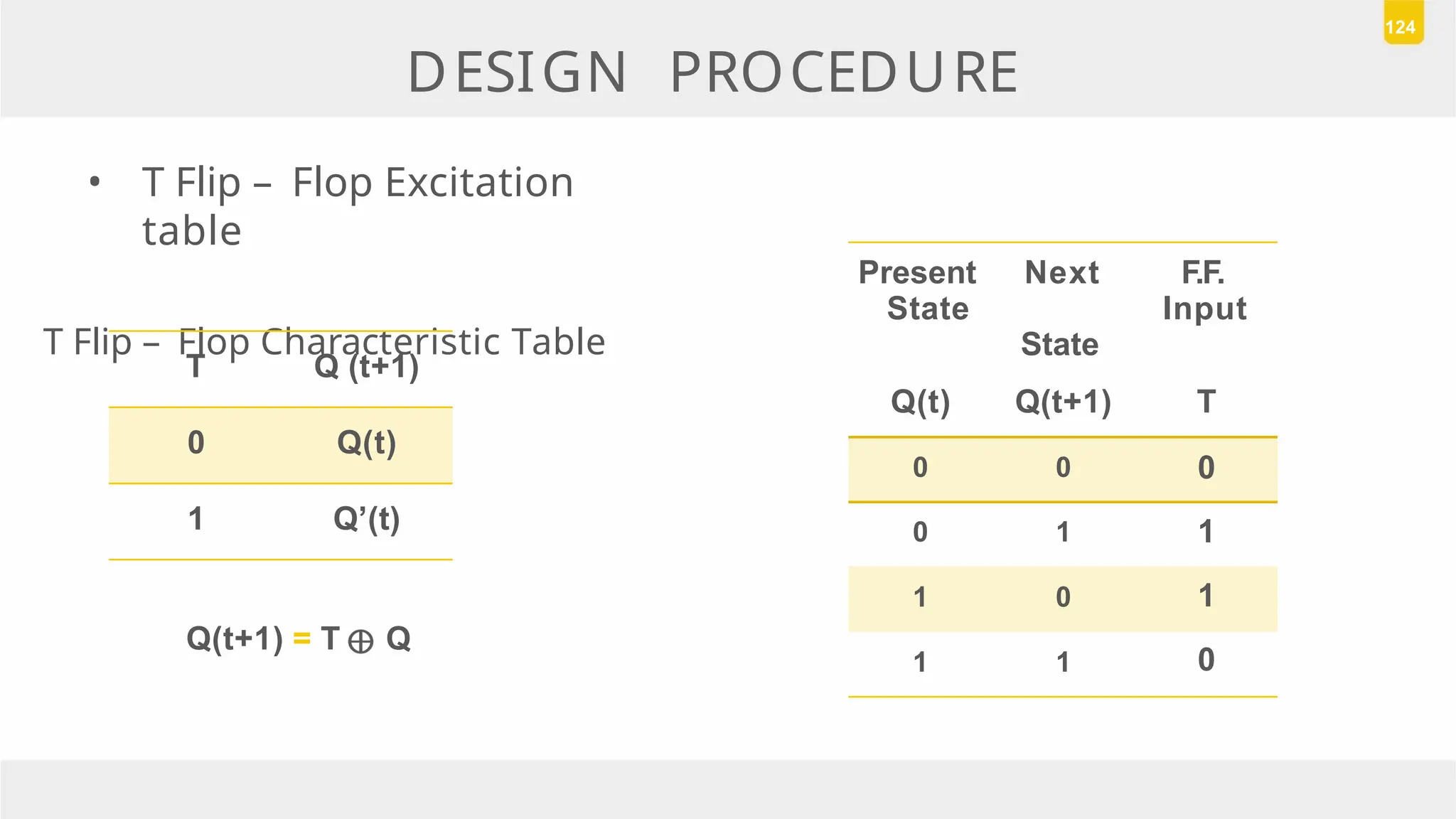

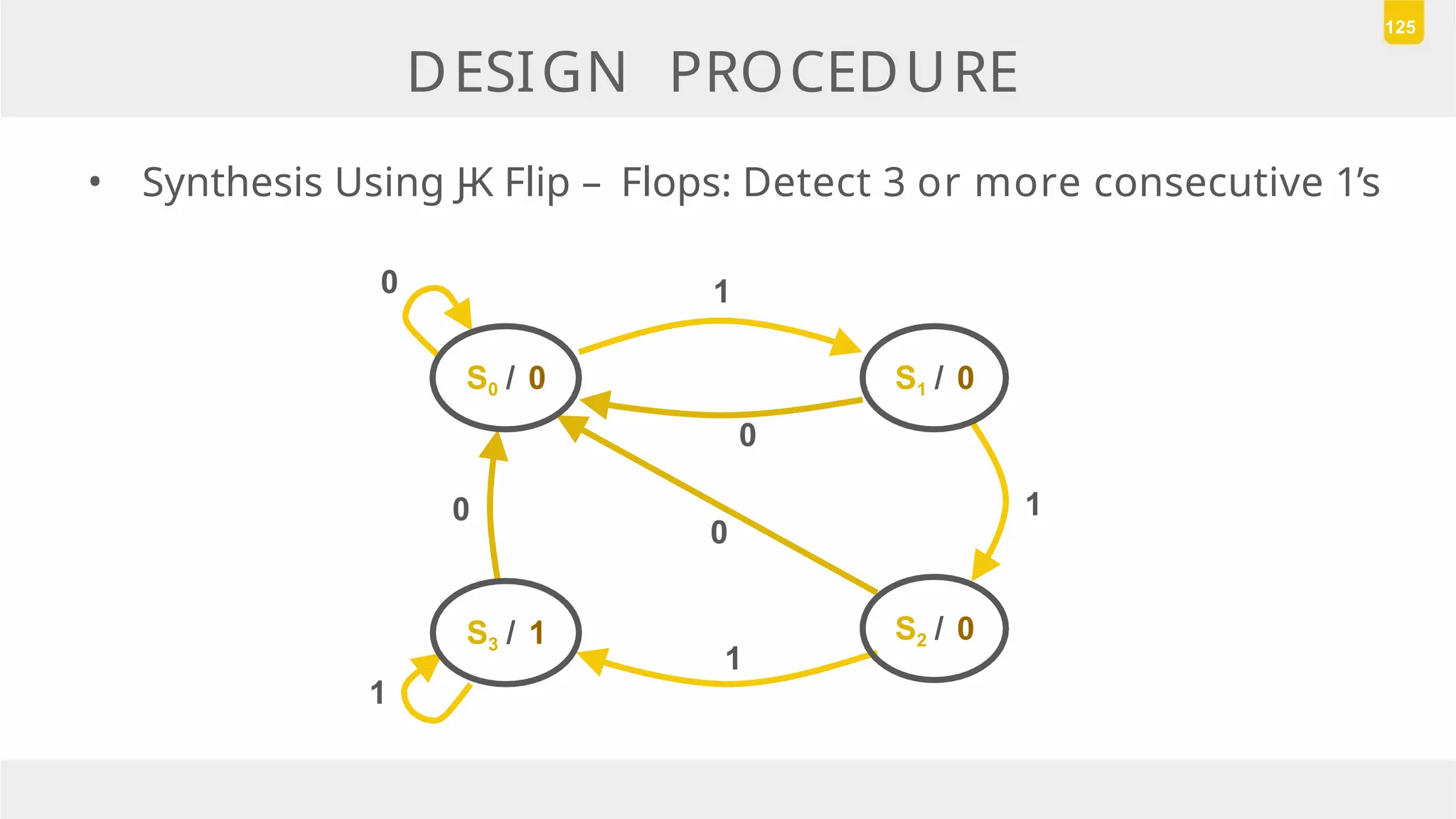

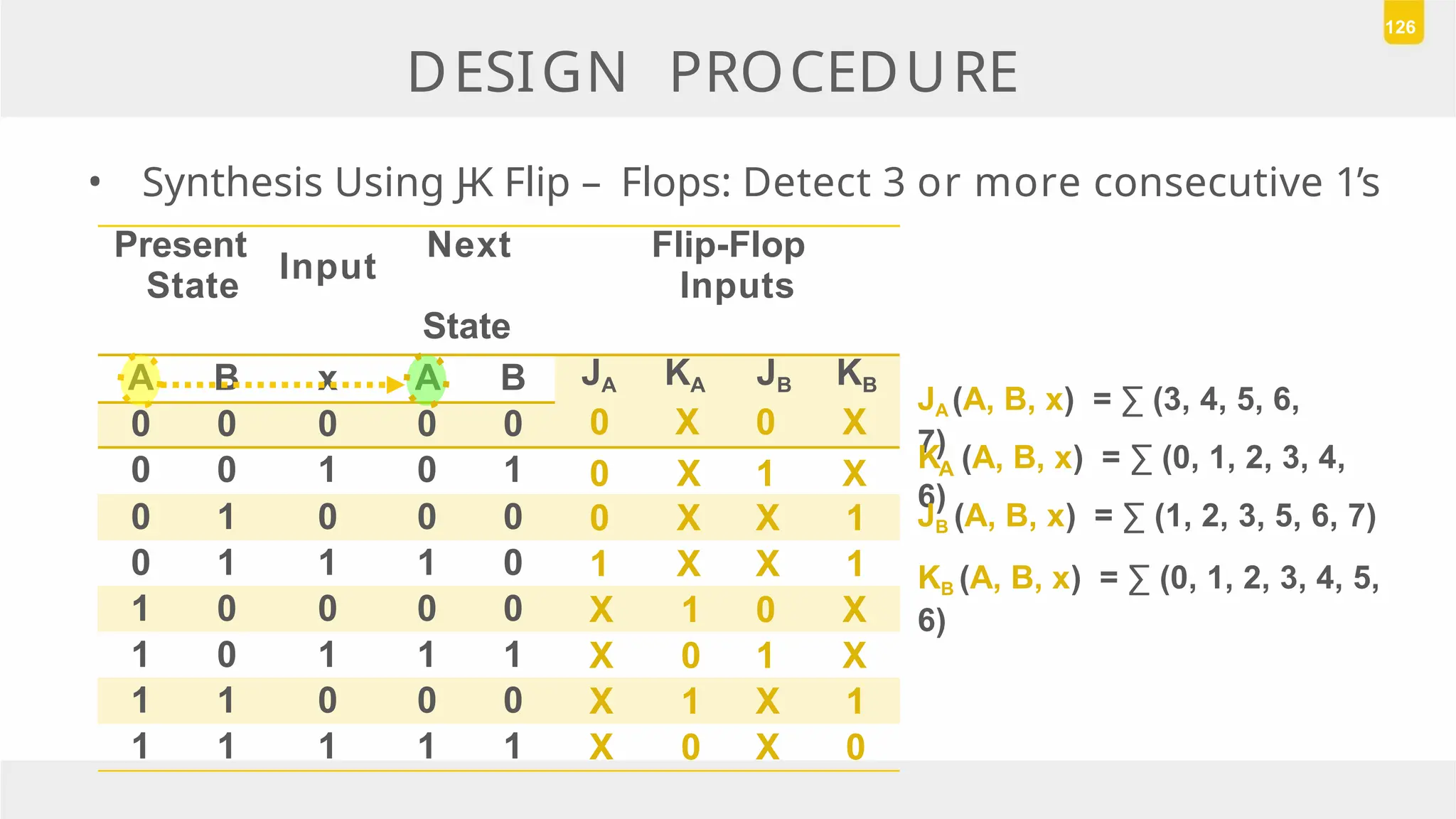

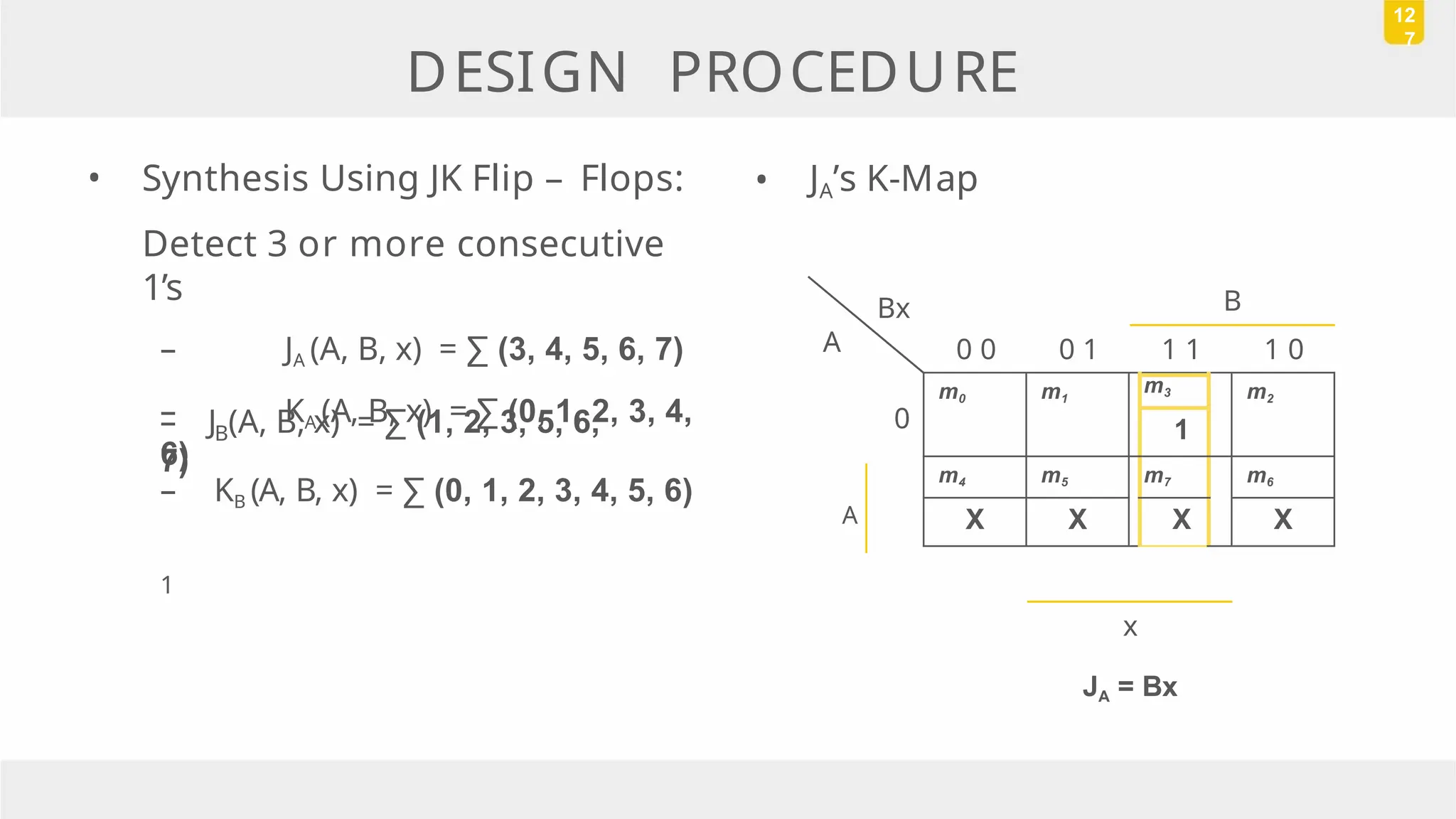

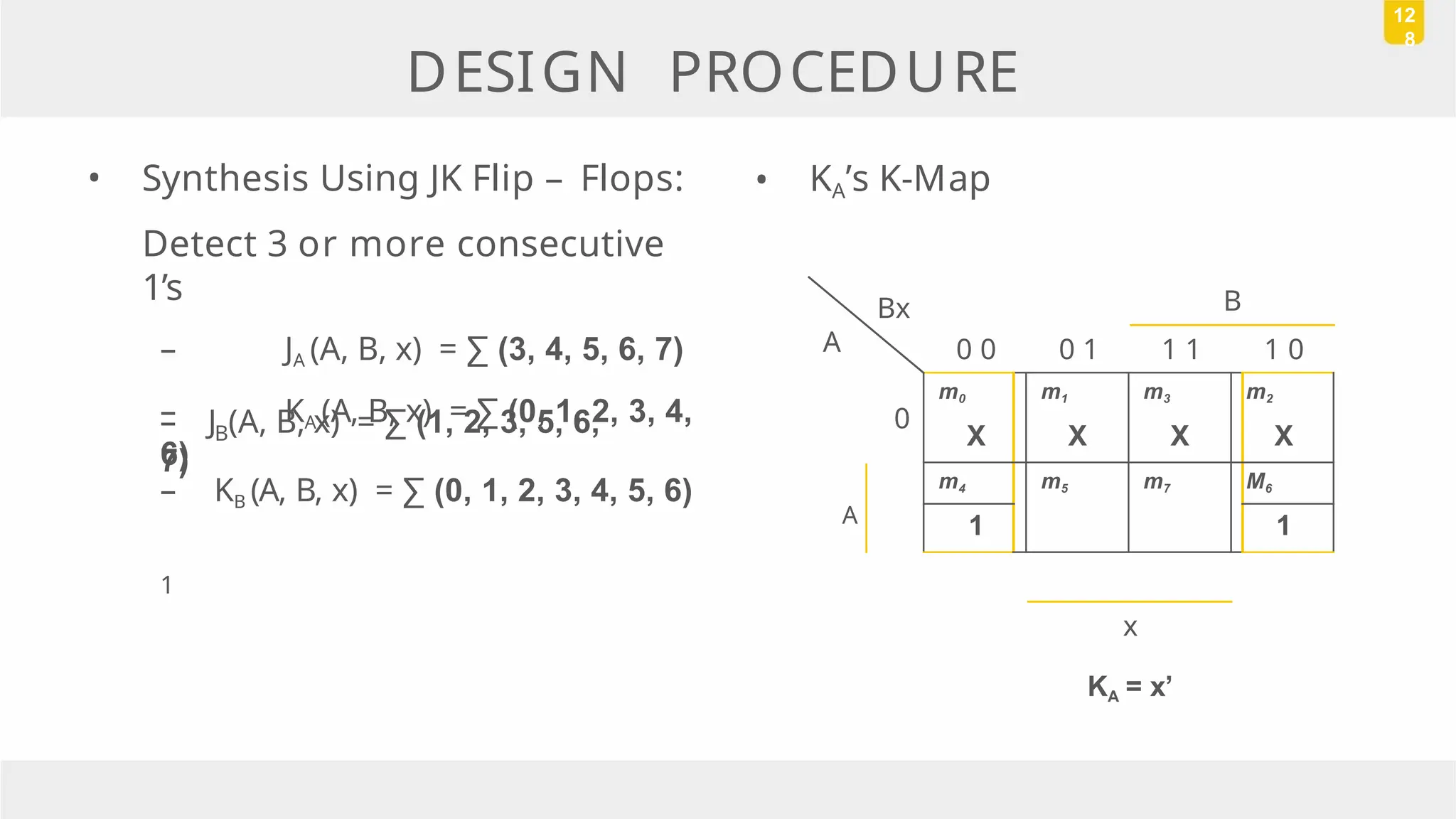

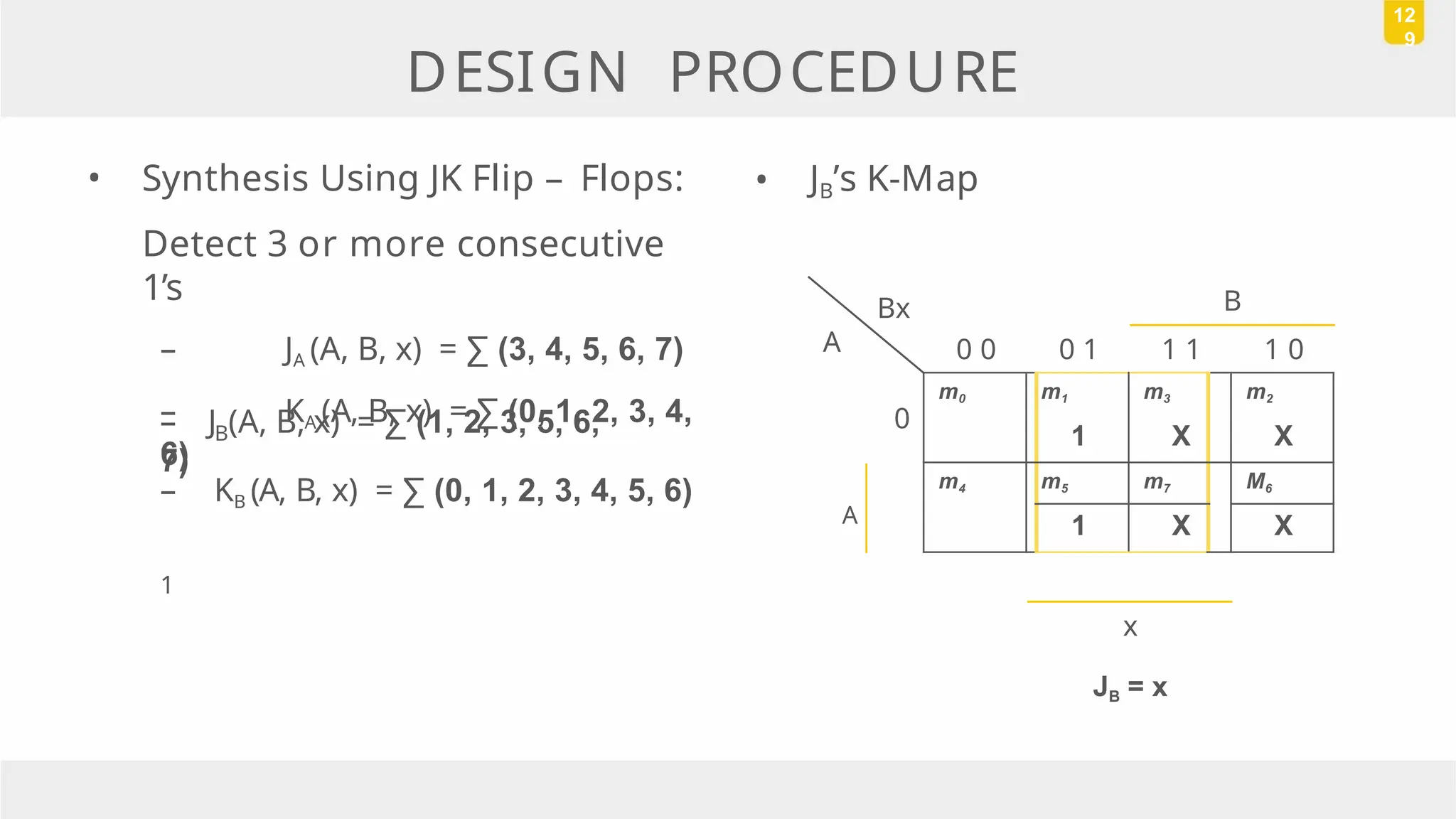

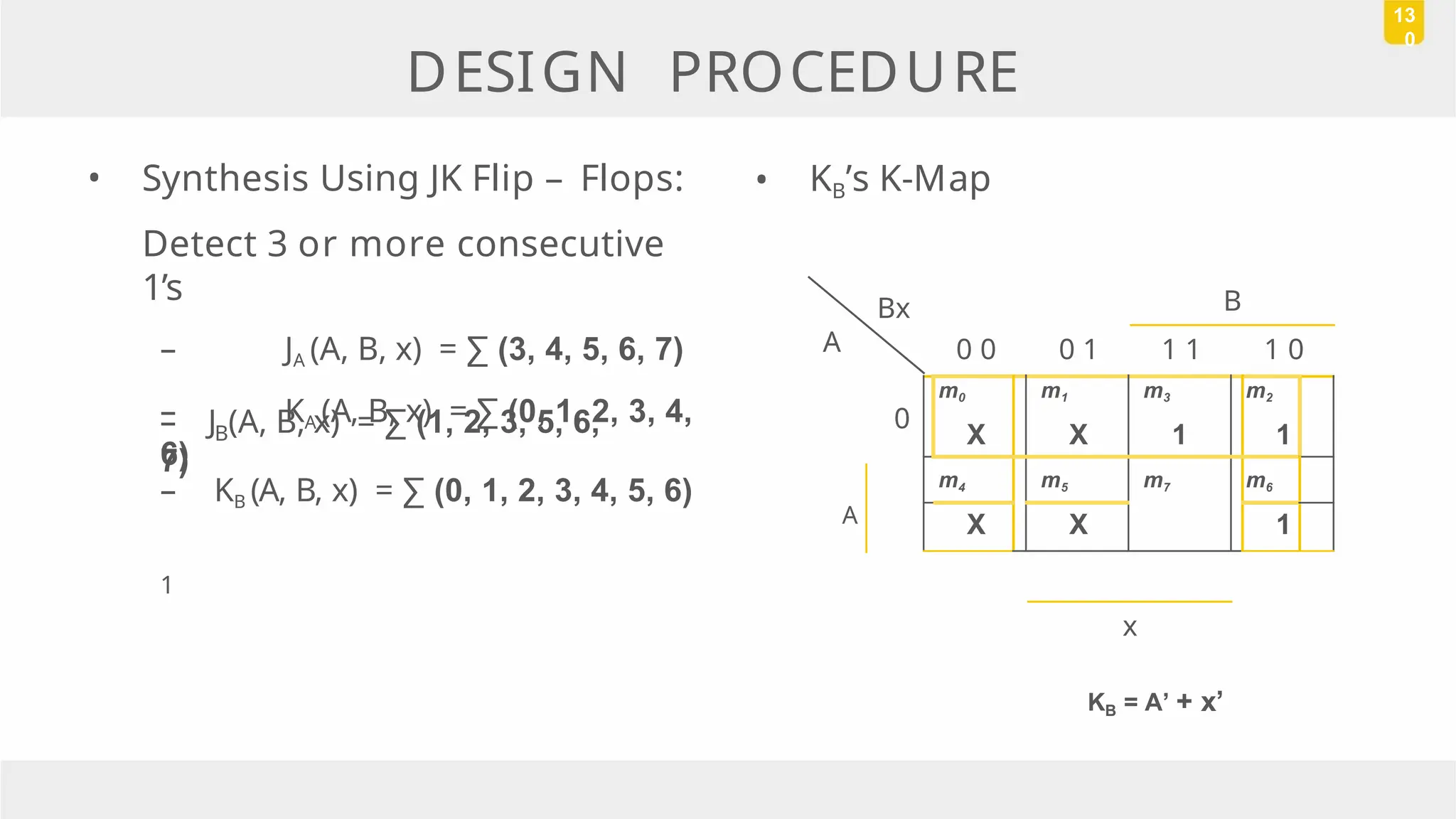

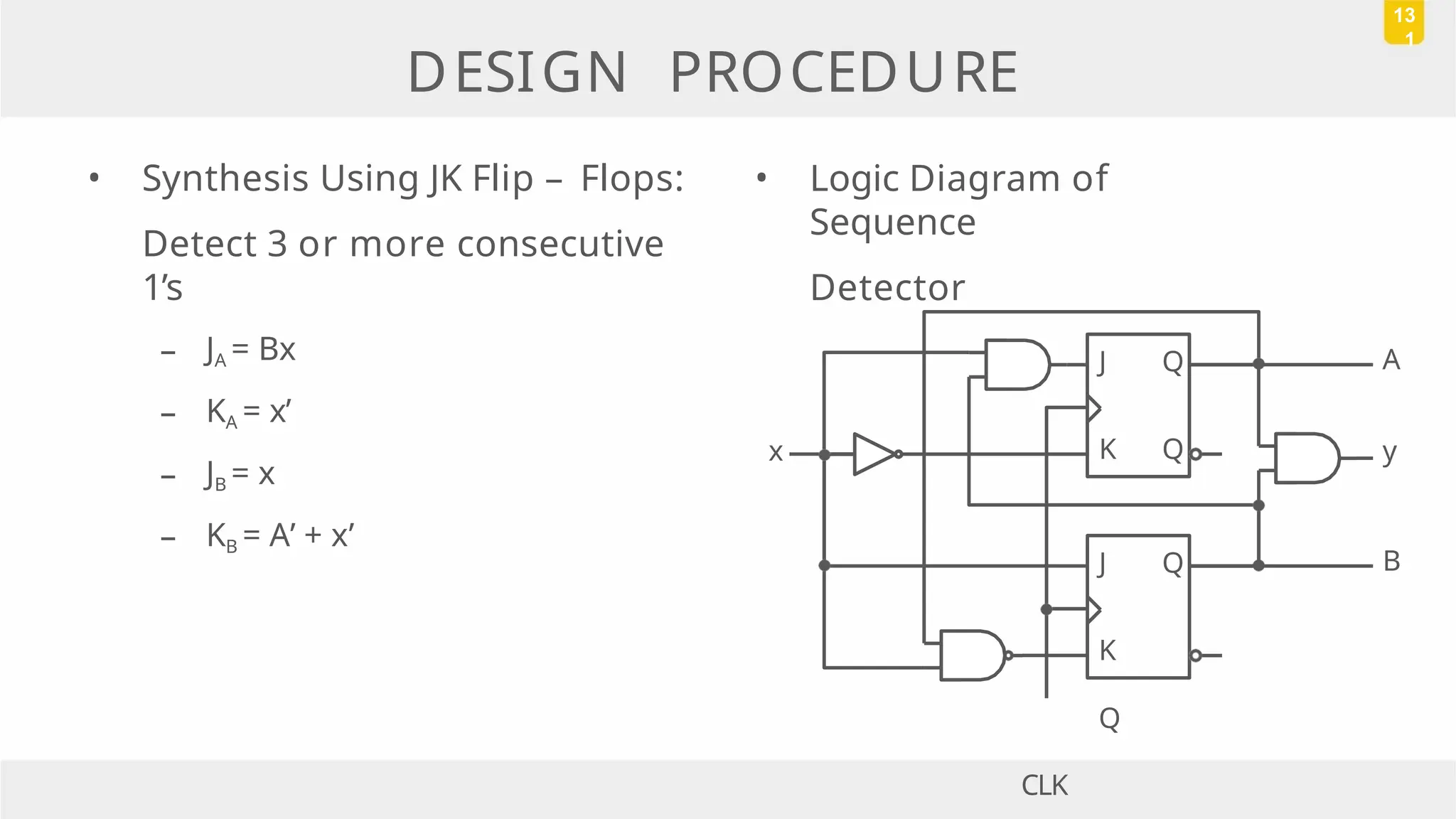

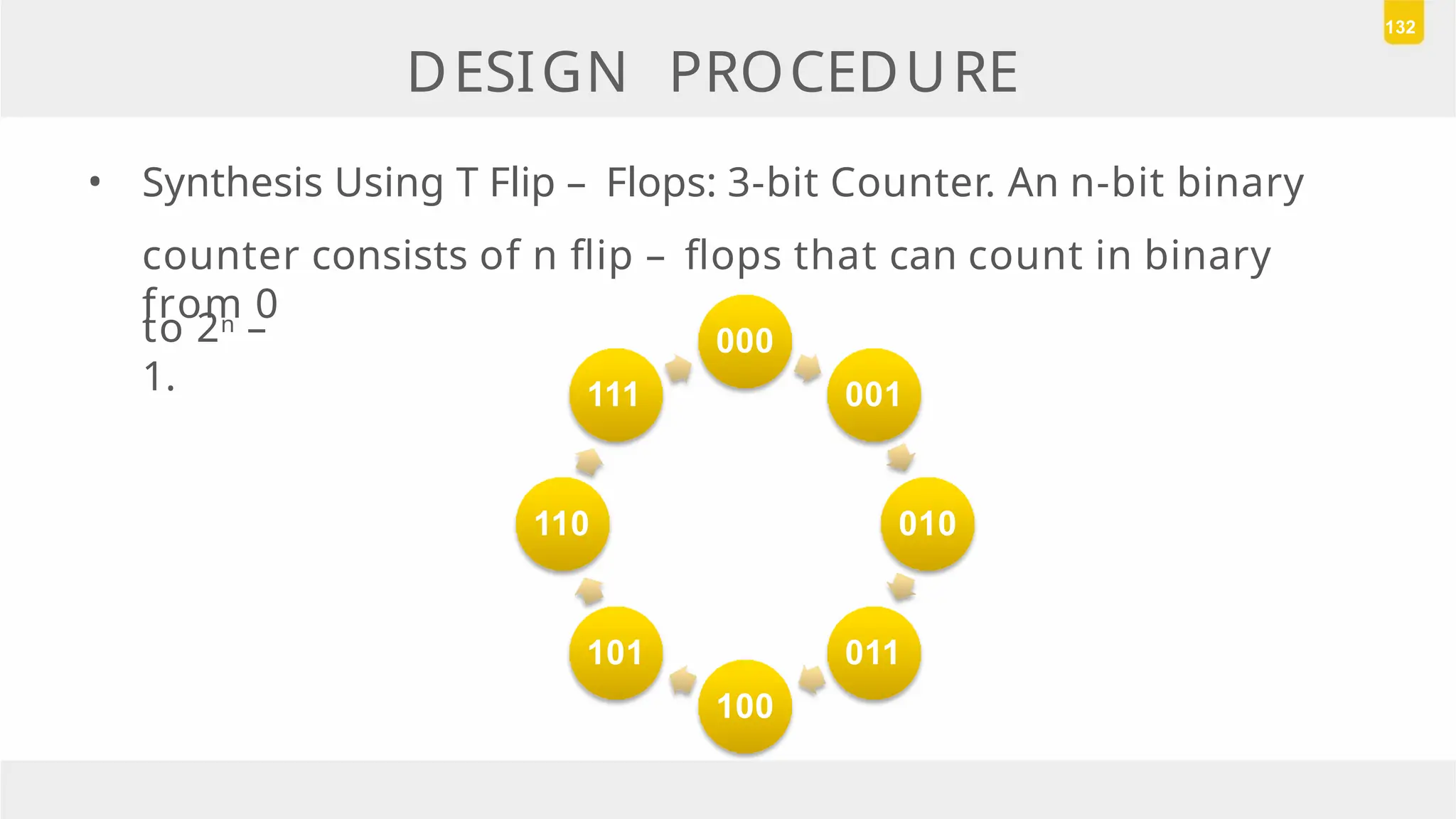

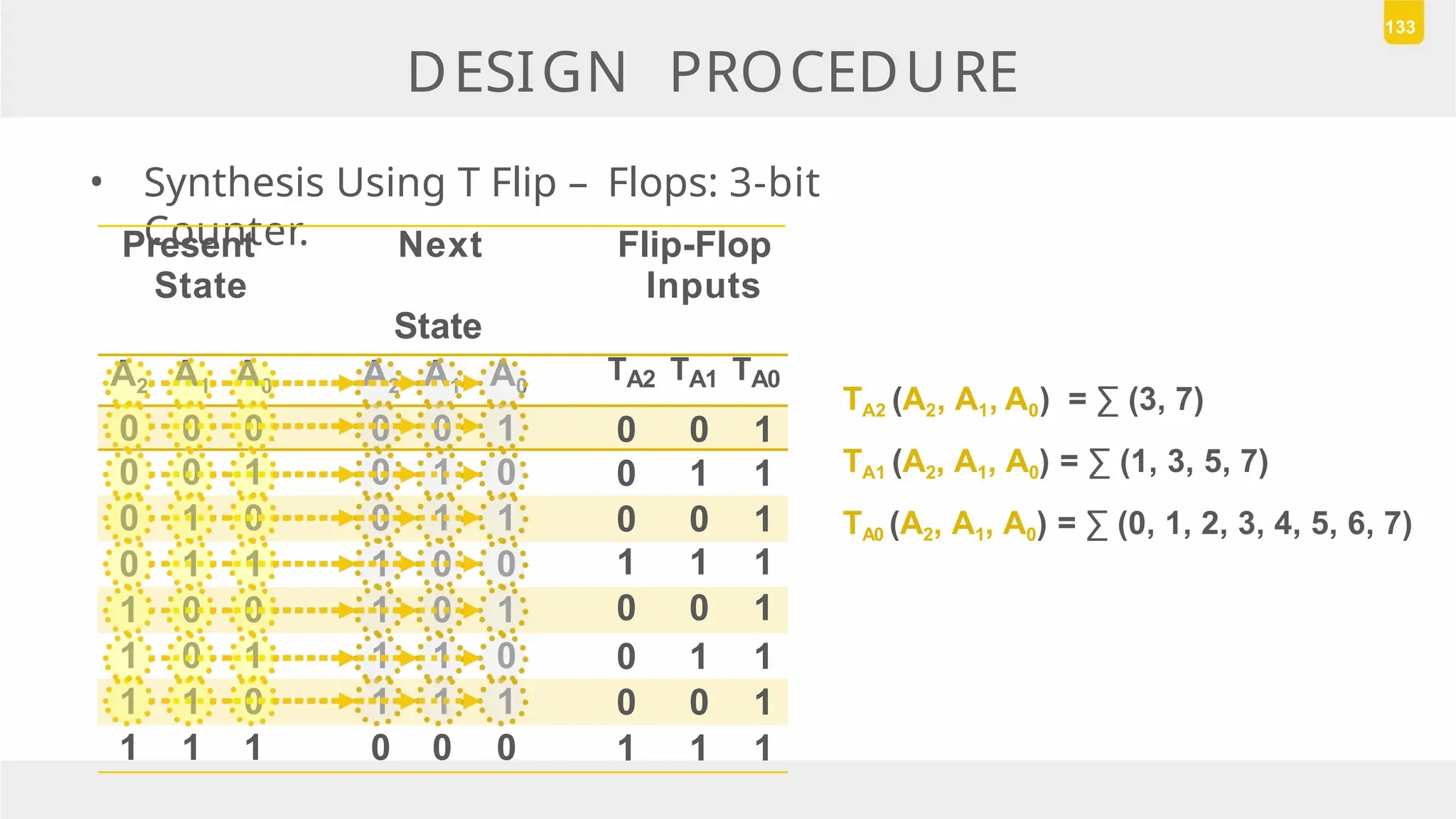

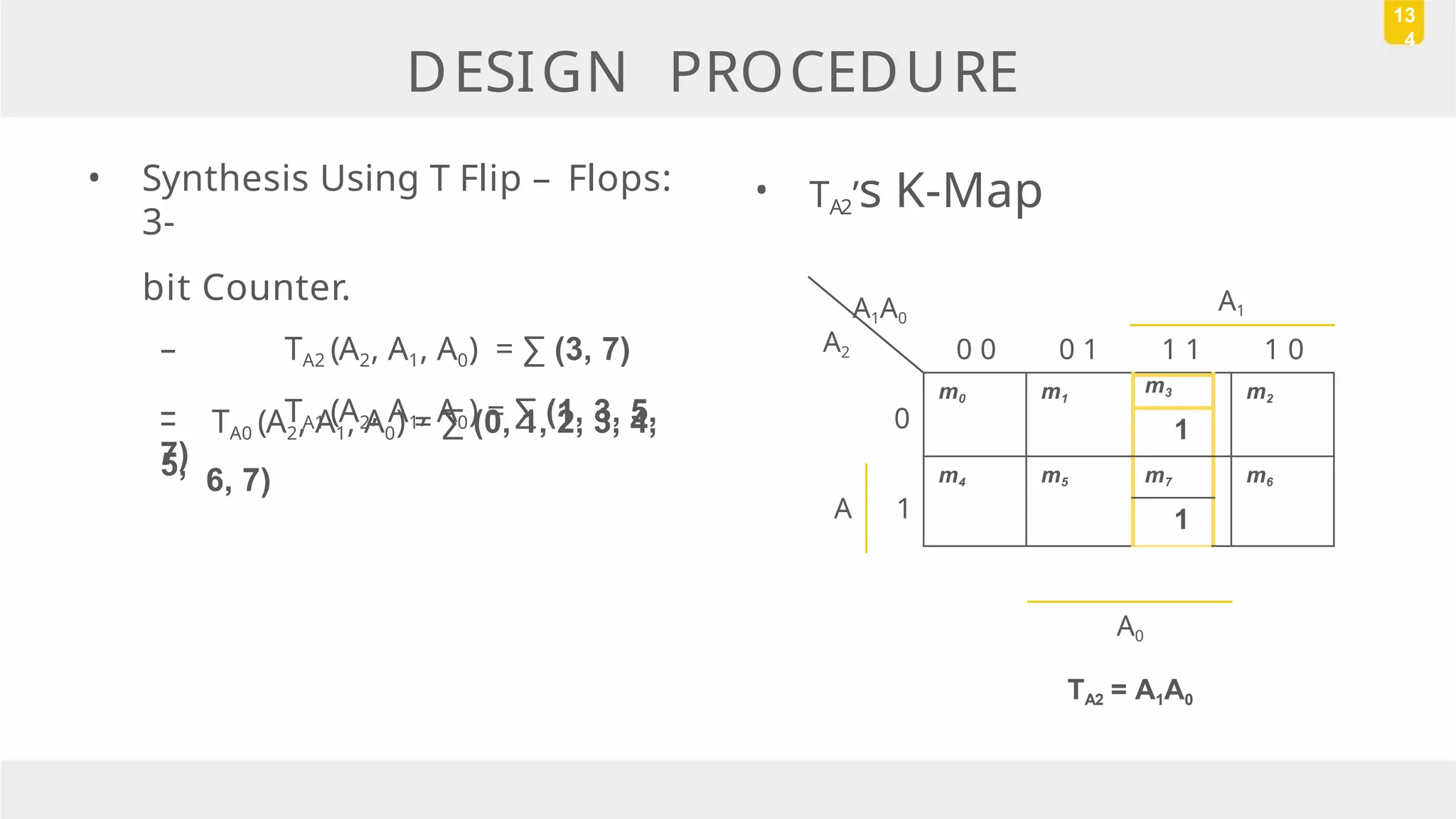

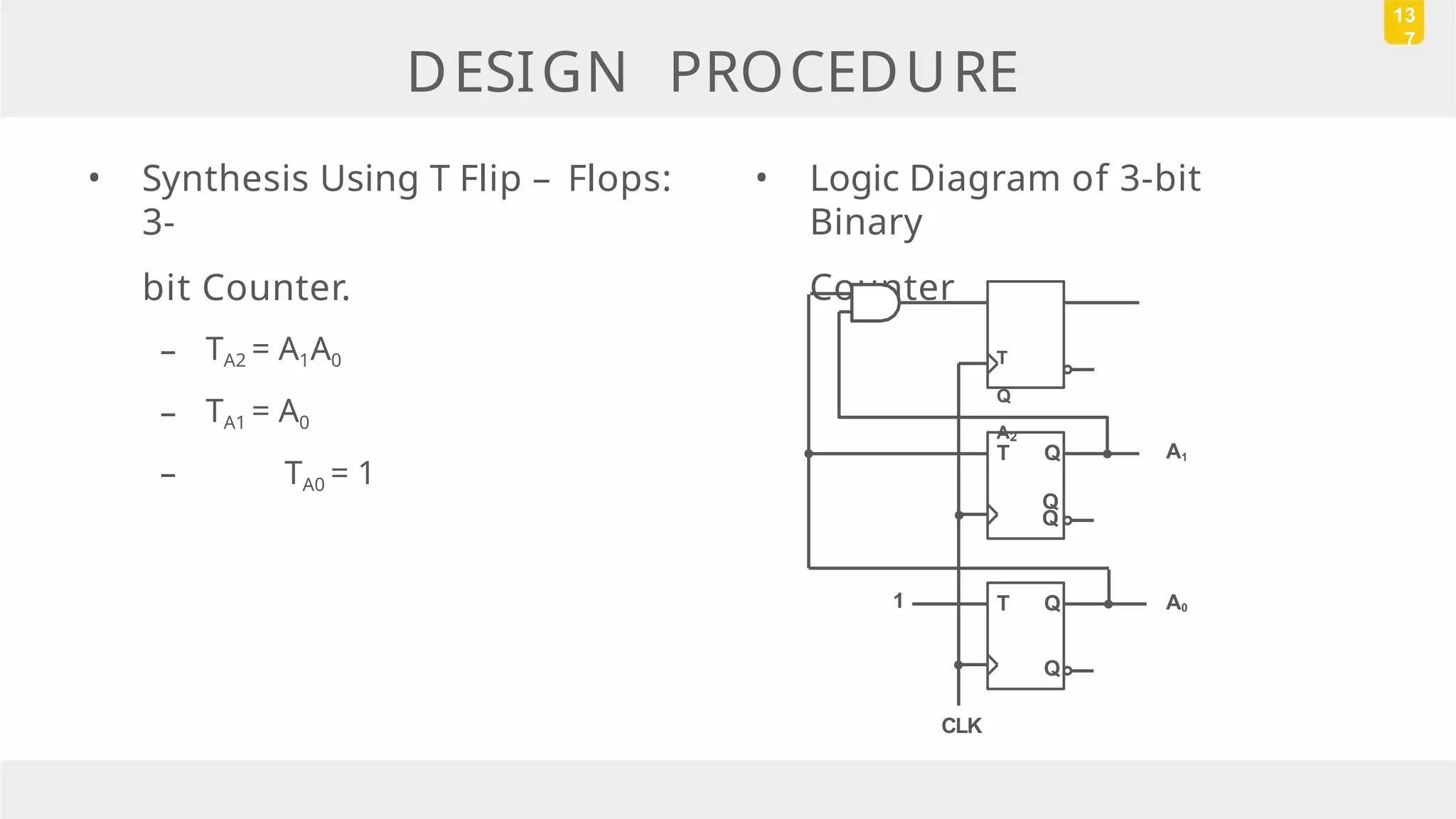

The document discusses state reduction and assignment in sequential circuits, highlighting methods to systematically check for state equivalence using implication tables. It emphasizes the importance of assigning binary values to states to minimize the cost of combinational circuits and outlines the design procedure of sequential circuits, including deriving state diagrams, reducing states, and using flip-flops for implementation. Various examples illustrate the design process and the synthesis of circuits that detect specific conditions, like three consecutive 1's.