Tipos de Memoria RAM

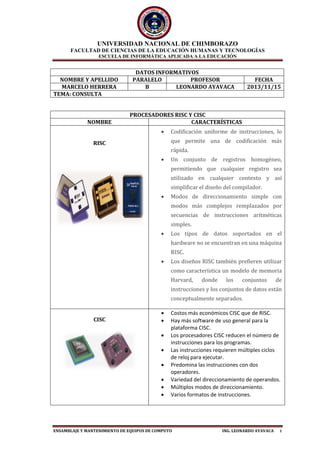

- 1. UNIVERSIDAD NACIONAL DE CHIMBORAZO FACULTAD DE CIENCIAS DE LA EDUCACIÓN HUMANAS Y TECNOLOGÍAS ESCUELA DE INFORMÁTICA APLICADA A LA EDUCACIÓN NOMBRE Y APELLIDO MARCELO HERRERA TEMA: CONSULTA NOMBRE DATOS INFORMATIVOS PARALELO PROFESOR B LEONARDO AYAVACA FECHA 2013/11/15 PROCESADORES RISC Y CISC CARACTERÍSTICAS • RISC • • • • Codificación uniforme de instrucciones, lo que permite una de codificación más rápida. Un conjunto de registros homogéneo, permitiendo que cualquier registro sea utilizado en cualquier contexto y así simplificar el diseño del compilador. Modos de direccionamiento simple con modos más complejos remplazados por secuencias de instrucciones aritméticas simples. Los tipos de datos soportados en el hardware no se encuentran en una máquina RISC. Los diseños RISC también prefieren utilizar como característica un modelo de memoria Harvard, donde los conjuntos de instrucciones y los conjuntos de datos están CISC • • • • • • • • conceptualmente separados. Costos más económicos CISC que de RISC. Hay más software de uso general para la plataforma CISC. Los procesadores CISC reducen el número de instrucciones para los programas. Las instrucciones requieren múltiples ciclos de reloj para ejecutar. Predomina las instrucciones con dos operadores. Variedad del direccionamiento de operandos. Múltiplos modos de direccionamiento. Varios formatos de instrucciones. ENSAMBLAJE Y MANTENIMIENTO DE EQUIPOS DE COMPUTO ING. LEONARDO AYAVACA 1

- 2. UNIVERSIDAD NACIONAL DE CHIMBORAZO FACULTAD DE CIENCIAS DE LA EDUCACIÓN HUMANAS Y TECNOLOGÍAS ESCUELA DE INFORMÁTICA APLICADA A LA EDUCACIÓN NOMBRE RISC CISC PROCESADORES RISC Y CISC VENTAJAS • La CPU trabaja más rápido al utilizar menos ciclos de reloj para ejecutar instrucciones. • Utiliza un sistema de direcciones no destructivas en RAM. Eso significa que a diferencia de CISC, RISC conserva después de realizar sus operaciones en memoria los dos operandos y su resultado, reduciendo la ejecución de nuevas operaciones. • Cada instrucción puede ser ejecutada en un solo ciclo del CPU. • Pocas instrucciones y muy básicas. • Formatos de instrucción uniformes. • • • • • NOMBRE RISC Facilidad de implementación del conjunto de instrucciones Compatibilidad hacia adelante y hacia atrás de nuevas CPU. Puede ser menor la complejidad del compilador. Computador con repertorio de instrucciones complejo. Gran número de instrucciones complejas. PROCESADORES RISC Y CISC DESVENTAJAS • Excesiva dependencia en la efectividad del compilador. • La depuración de los programas se hace dficil por la programación de instrucciones. • Se incrementa el temaño del código de lenguaje maquina. • Necesidad de memoria rápida. ENSAMBLAJE Y MANTENIMIENTO DE EQUIPOS DE COMPUTO ING. LEONARDO AYAVACA 2

- 3. UNIVERSIDAD NACIONAL DE CHIMBORAZO FACULTAD DE CIENCIAS DE LA EDUCACIÓN HUMANAS Y TECNOLOGÍAS ESCUELA DE INFORMÁTICA APLICADA A LA EDUCACIÓN CISC • • • SIGLAS DRAM FPM La complejidad del conjunto de instrucciones crece Las instrucciones de longitud variable reducen el rendimiento del sistema Inclusión de instrucciones que raramente se usan. TIPOS DE MEMORIAS RAM NOMBRE DESCRIPCIÓN Es la memoria de trabajo, también llamada RAM, esta organizada en direcciones que son reemplazadas muchas veces por segundo. Random (Dynamic Access Memory) (Fast Page Mode) ENSAMBLAJE Y MANTENIMIENTO DE EQUIPOS DE COMPUTO Esta memoria llegó a alcanzar velocidades de 80 y 70 nanosegundos (ns). Hasta hace aproximadamente un año ésta memoria era la más popular, era el tipo de memoria normal para las computadores 386, 486 y los primeros Pentium®, llegó a fabricarse en velocidades de 60ns. ING. LEONARDO AYAVACA 3

- 4. UNIVERSIDAD NACIONAL DE CHIMBORAZO FACULTAD DE CIENCIAS DE LA EDUCACIÓN HUMANAS Y TECNOLOGÍAS ESCUELA DE INFORMÁTICA APLICADA A LA EDUCACIÓN EDO SIGLAS (Extended Data Output) NOMBRE RDRAM Esta memoria fue una innovación en cuestión de transmisión de datos pudiendo alcanzar velocidades de hasta 45ns, dejando satisfechos a los usuarios. DESCRIPCIÓN Esta memoria tiene una transferencia de datos de 64 bits que se pueden producir en ráfagas de 2ns, además puede alcanzar taza de tranferencia de 533 Mhz con picos de 1.6Gb/s. (Rambus DRAM) SDRAM (Synchronous DRAM) Esta memoria funciona como su nombre lo indica, se sincroniza con el reloj del procesador obteniendo información en cada ciclo de reloj, sin tener que esperar como en los casos anteriores. WEBGRAFÍA http://marindelrio.wordpress.com/2013/03/07/arquitecturas-risc-y-cisc/ http://rcmcomputointegrado.blogspot.com/2012/03/arquitectura-risc-y-cisc.html http://www.slideshare.net/gustavodavila2309/tema-4-9770552 http://www.info-ab.uclm.es/labelec/solar/Memoria/Tipos%20de%20Memoria%20RAM.htm ENSAMBLAJE Y MANTENIMIENTO DE EQUIPOS DE COMPUTO ING. LEONARDO AYAVACA 4