Verilog data types -For beginners

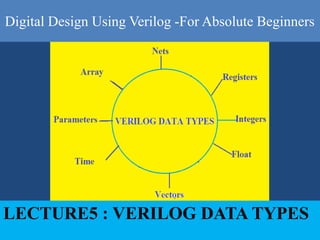

- 1. Digital Design Using Verilog -For Absolute Beginners LECTURE5 : VERILOG DATA TYPES

- 2. Introduction •Verilog is a powerful HDL used to design & verify the digital systems. •So, to describe the hardware of a system several types of data variables are required. •For ex; to describe a signal, its type must be specified , like bit type , which means that the signal can have only either 0 or 1, or type std _ logic, in which the signal can be assigned a value out of four possible values which include 0, 1, unknown(x) and high impedance (z) .

- 3. VERILOG-DATA TYPES • There are two important data types: (i).the variable data types and (ii). net data types. • These two groups differ in the way that they are assigned and hold values.They also represent different hardware structures. • The net data types shall represent physical connections between structural entities, such as gates. • A net shall not store a value (except for the trireg net). Instead, its value shall be determined by the values of its drivers, such as a continuous assignment or a gate.21 June 2020 3yayavaram@yahoo.com

- 4. Declaration of ‘net’ • Nets are declared by the predefined word ‘wire’. Nets have values that change continuously by the circuits that are driving them. • Verilog supports four values for nets. They are 21 June 2020 4yayavaram@yahoo.com

- 5. contd • Examples of net types are wire a; wire sum; wire S1 = 1’b0; similarly wire S2= 4’b0101 • The second statement declares a net by the name sum. • The third statement declares a net by the name of S1 ; its initial value is 1’b0, which represents 1 bit with value 0. • Similarly ,initial value of S2 is 4 bit with value 0101 21 June 2020 5yayavaram@yahoo.com

- 6. contd • A wire does not store its value. It must be driven in one of two ways: (i).By connecting the wire to the output of a gate or module (ii).By assigning a value to the wire in a continuous assignment. wire y : assign y = a & b; 21 June 2020 6yayavaram@yahoo.com

- 7. Contd • By default Nets are 1-bit values. But it can be a vector also. • For ex: wire [31:0]bus ; Here the size of the bus is 32 bit vector and it is a wire type. • All unconnected nets are set to ‘z’.(High impedance) • Also wire is always input , for standard interconnection. • Nets are used to model connections between continuous assignments and instantiations. 21 June 2020 7yayavaram@yahoo.com

- 8. Example module mymux2_1(A,B,S,Y); //Port declaration output y; input A,B,S; //internal variable declarations Wire S1,A1,B1; not (S1,S); and1 (A1,A,S1); and2 (B1,B,S); Or(Y,A1,B1); endmodule21 June 2020 8yayavaram@yahoo.com

- 9. contd • In the example, S, A1,B1 are declared as Wire. • Because they denote the interconnections and they are continuously driven by NOT,AND1 and AND2 gates. • By default they assume bit values.(either o or 1). 21 June 2020 9yayavaram@yahoo.com

- 10. Different Net Types • Verilog supports different net types for synthesis. They are i. wire ii. wor (wired or) iii.Wand (wired and) iv.Tri (tristate) v.supply0 (gnd) vi.supply1 (Vdd). • Here wire and Tri state serve the same purpose. • s. 21 June 2020 10yayavaram@yahoo.com

- 11. contd • The net types wire and tri shall be identical in their syntax and functions; • Two names are provided so that the name of a net can indicate the purpose of the net in that model. • A wire net can be used for nets that are driven by a single gate or continuous assignment. • The tri net type can be used where multiple drivers drive a net.. 21 June 2020 11yayavaram@yahoo.com

- 12. Different Types of Nets. • wor /wand inserts an or/and gate at the connection as shown below. • Suppose we have a connection shown below. • The simulator will give an error . • So, if we use wand (wired and) the synthesis tool during synthesis will add an add gate as shown below. Similarly ,if wor is used an or gate is added at the connection,which solves the conflict. • s.21 June 2020 12yayavaram@yahoo.com

- 13. Different Net Types • wired and(wand circuit) wired or (wor circuit) • s. 21 June 2020 13yayavaram@yahoo.com

- 14. Ex: Supply 0 & Supply1 21 June 2020 14yayavaram@yahoo.com • Normally, the during the synthesis, the tool will consider Supply0 as ground and Supply1 as Vdd. • Let us consider an example. module supply_ex(A,B,C,Y); input A,B,C; output Y; wire t1,t2; supply0 gnd; supply1 Vdd;

- 15. contd 21 June 2020 15yayavaram@yahoo.com nand1(t1,Vdd,A,B); X-or2(t2,C, gnd); and3(Y,t1,t2); endmodule So, the tool during the synthesis, will treat the supply0 as ground and Supply1 as Vdd.

- 16. REGISTER(Reg) • Register, in contrast to nets, stores values until they are updated. Register, as its name suggests, represents data-storage elements. Register is declared by the predefined word reg. • Verilog supports four values shown below, for register 21 June 2020 16yayavaram@yahoo.com

- 17. contd • Different register types are supported by Verilog for Synthesis. • Reg (register) • integer • General rule of thumb is,reg is used to model actual hardware registers such as Counters, Accumulators etc. • Integer is used for situations like loop counting. • By default the size of the register is bit • Ex: reg x,y21 June 2020 17yayavaram@yahoo.com

- 18. VECTORS • Vectors are multiple bits. A register or a net can be declared as a vector. • Vectors are declared by brackets [ ]. • Examples of vectors are: • wire [31:0] a = 32’b1010; • reg [7:0] total = 8’d12; • The first statement declares a net a. It has 32 bits, and its initial value is 00…1010 (b stands for bit). The second statement declares a register total. • Its size is eight bits, and its value is decimal 12 (d stands for decimal).21 June 2020 18yayavaram@yahoo.com

- 19. Real • Floating point values are denoted by Real. • These Real (floating-point) numbers are declared with the predefined word ‘ real ‘. • Examples of real values are 2.4, 56.3, and 5e12 ( • The value 5e12 is equal to 5 × 1012. • The following statement declares the register weight as real: • real weight; 21 June 2020 19yayavaram@yahoo.com

- 20. Parameter • A parameter represents constant value symbolically. • The definition for a parameter consists of the parameter name and the value assigned to it. • The value can be any constant-valued integer or Boolean expression. • If you do not set the size of the parameter with a range definition or a sized constant, the parameter is unsized and by default it is a 32-bit quantity 21 June 2020 20yayavaram@yahoo.com

- 21. Example module my_comp1 (X, Y, xgty, xlty, xeqy); parameter N = 3; input [N:0] X, Y; output xgty, xlty, xeqy; wire [N:0] sum, Y; To change the size of the inputs x and y, the size of the nets sum, and the size of net Y to eight bits, the value of N is changed to seven as: • parameter N = 7 21 June 2020 21yayavaram@yahoo.com

- 22. ARRAYS Verilog, in contrast to VHDL, does not have a predefined word for array. • Registers and integers can be written as arrays. For example: • parameter N = 4; • parameter M = 3; • reg signed [M:0] carry [0:N]; • The above statements declare an array by the name carry. The array carry has five elements, and each element is four bits. The four bits are in two’s complement form. For example, if the value of a certain element is 1001, then it is equivalent to decimal –7.21 June 2020 22yayavaram@yahoo.com

- 23. Time-variable 21 June 2020 23yayavaram@yahoo.com • A time variable is used for storing and manipulating simulation time quantities in situations where timing checks are required and for diagnostics and debugging purposes. • This data type is typically used in conjunction with the $time system function.

- 24. INTEGERS 21 June 2020 24yayavaram@yahoo.com • An integer is a general-purpose variable used for manipulating quantities that are not regarded as hardware registers i.e for loops-indicies, parameters, and constants. • They are of implicitly of type reg. However they store data as signed numbers whereas explicitly declared reg types store them as unsigned. • The default size of Integer is 32-bits. • If they hold constants, the synthesis tool will adjusts them to the minimum width needed at compilation.

- 25. contd • An integer declaration uses the integer keyword and specifies a list of variables. • integer a, b; //two integers • integer c [1:10]; // an array of integers. • integer data; // integer • integer i, j, k; // multiple integers • An integer is a general purpose 32-bit variable. Operations on it are assumed to be two's complement and the most significant bit indicates the sign. 21 June 2020 25yayavaram@yahoo.com