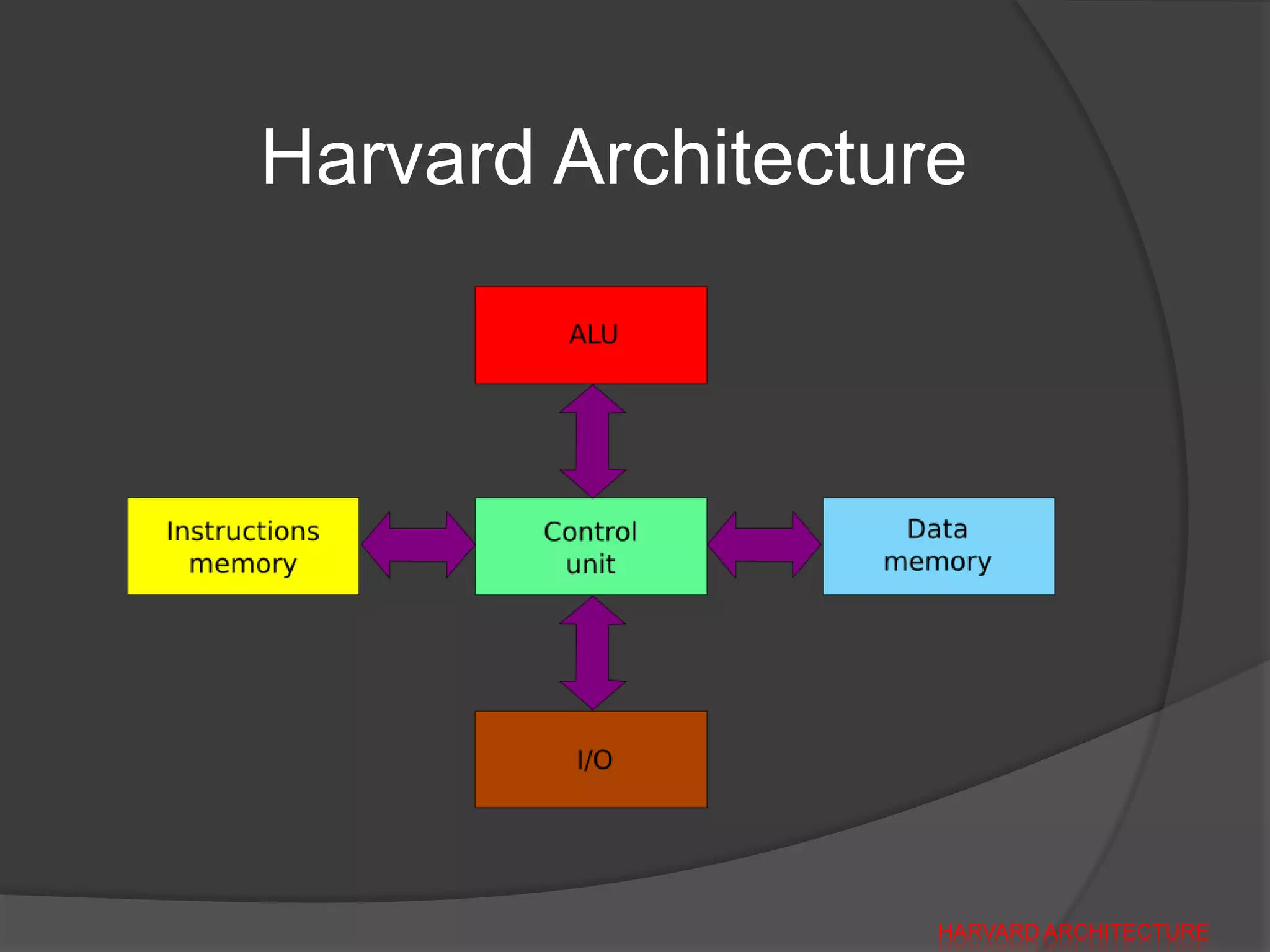

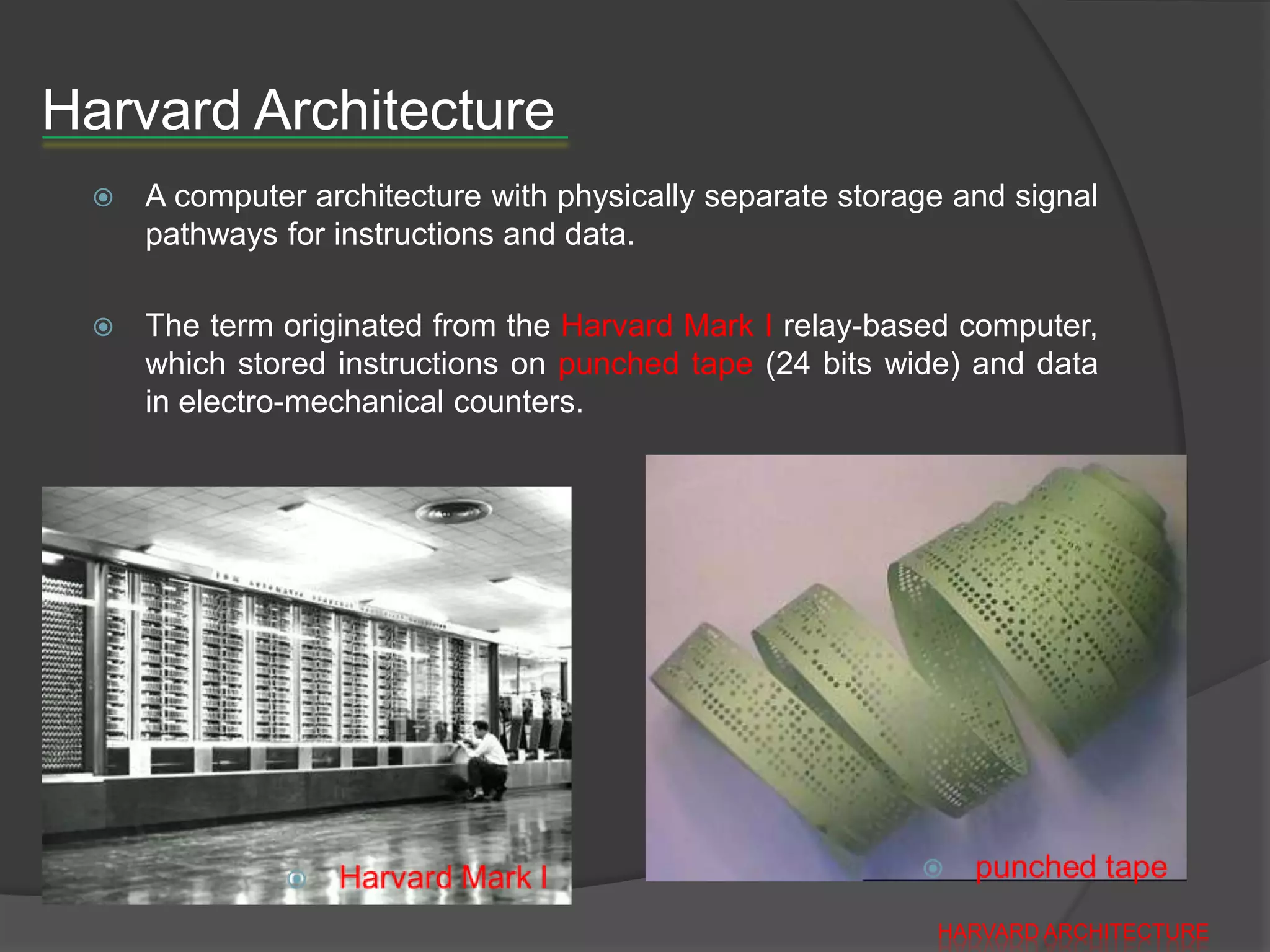

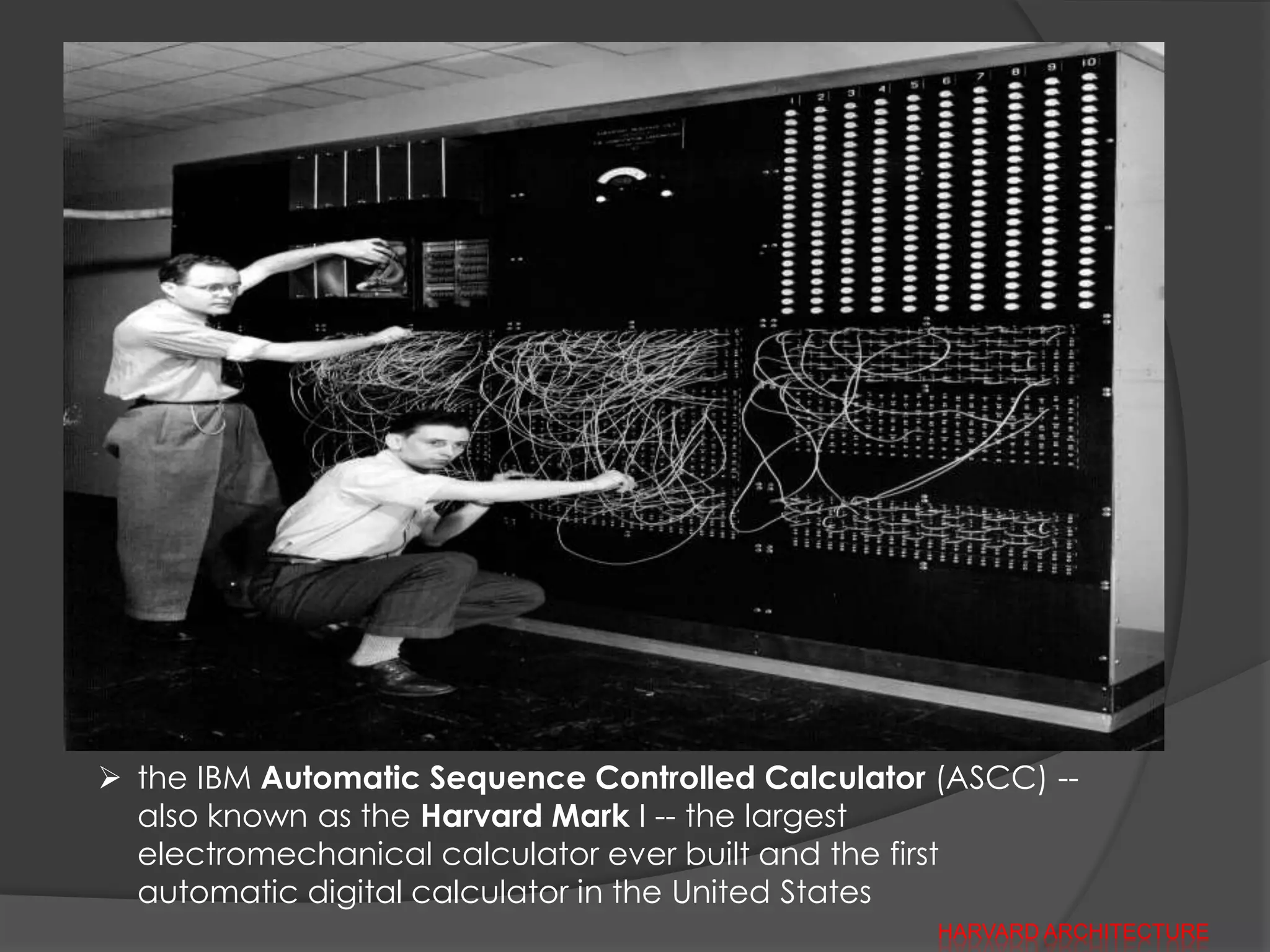

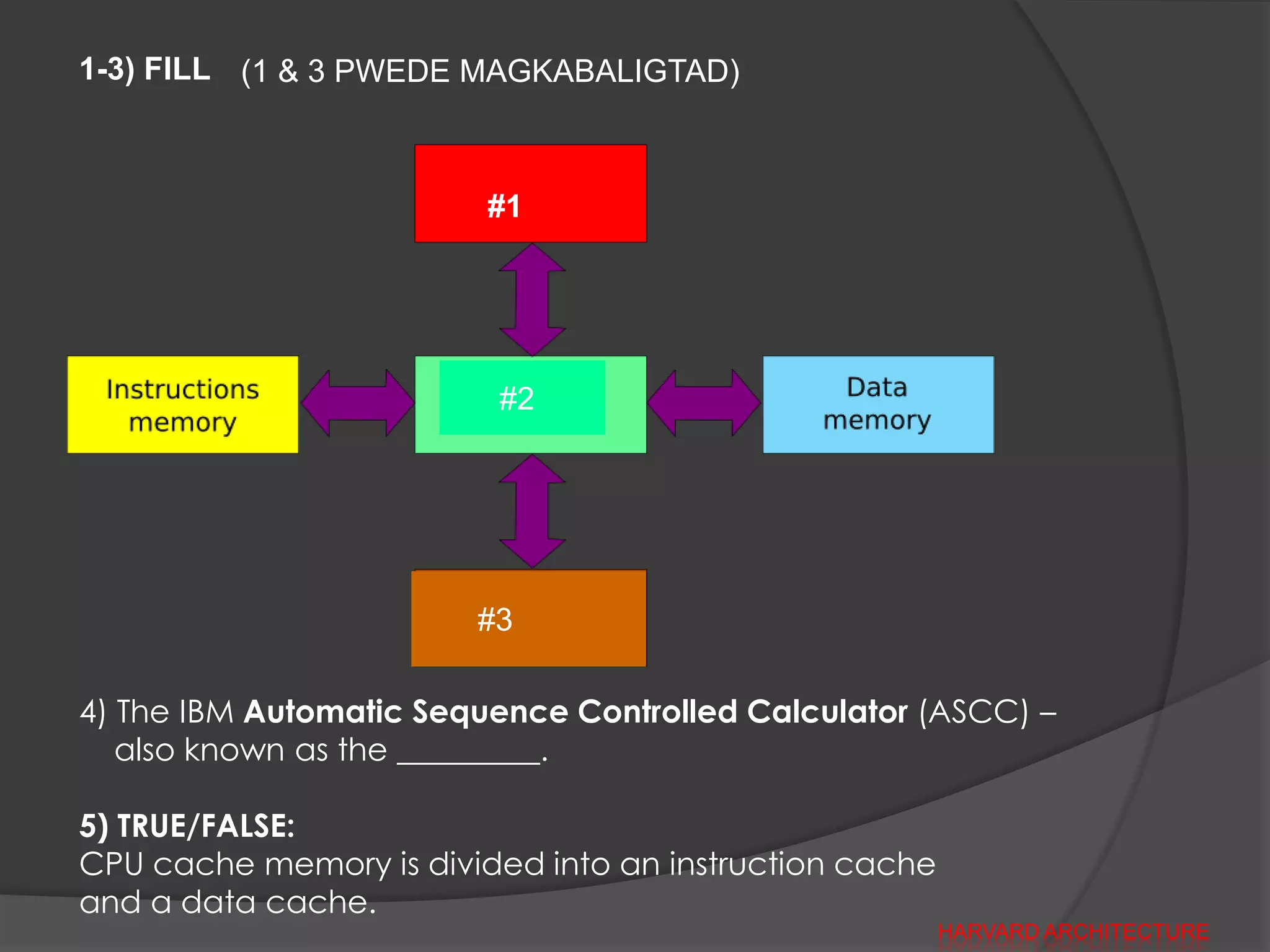

The Harvard architecture stores instructions and data in separate physical memory units. It originated from the Harvard Mark I computer which stored instructions on punched tape and data in electromechanical counters. In the Harvard architecture, the instruction and data memories can differ in width, timing, technology and addressing structures. Modern CPU designs often use a modified Harvard architecture, where the CPU contains separate instruction and data caches to enable high performance despite slower main memory access times.